VHDL 의 기본

VHDL 의 기본. Lecture #4. 강의 내용. VHDL 의 기본 VHDL 문장 VHDL 모델링. 1. VHDL 의 기본. VHDL 의 기본 - 강의순서. VHDL Lexical Elements VHDL Design Description Object Data Type Attribute Operator Statements Concurrent vs. Sequential Statements. VHDL 어휘 요소 (1). 주석 (comment)

VHDL 의 기본

E N D

Presentation Transcript

VHDL의 기본 Lecture #4

강의 내용 • VHDL의 기본 • VHDL 문장 • VHDL 모델링 모바일컴퓨터특강

VHDL의 기본 - 강의순서 • VHDL Lexical Elements • VHDL Design Description • Object • Data Type • Attribute • Operator • Statements • Concurrent vs. Sequential Statements 모바일컴퓨터특강

VHDL 어휘 요소 (1) • 주석(comment) • 연자부호(‘-’)를 연속적으로 2개(‘—’)로 시작하는 문장 • 예: entity AND_OR is -- Entity declaration port( A, B, C : in std_logic; Y : OUT std_logic); end AND_OR; • 식별어(Identifier) • 신호명, 변수명, 엔티티 이름 등과 같이 VHDL에서 식별 목적으로 사용하는 공백을 갖지 않는 문자열 • 대소문자 구분하지 않음 모바일컴퓨터특강

VHDL 어휘 요소 (2) • 식별어(Identifier) (계속) • 식별어 작성법 • 식별어는 영문자, 숫자 그리고 밑줄(‘_’)로 구성 • 식별어는 반드시 영문자로 시작해야 한다 • 식별어는 밑줄로 시작 또는 끝이 나면 안된다 • 식별어는 연속적으로 밑줄을 포함해서는 안된다 • 사용 예: Counter, next_value, s_1, s_2, generate_read_cycle • 잘못 사용 예: last-value, _a0, a0_, clock__pulse, 4bit_counter 모바일컴퓨터특강

VHDL 어휘 요소 (3) • 지정어(keyword) • VHDL 구문을 위해 미리 지정된 문자열 • 대소문자 구분 없으며, 식별자로 사용할 수 없다 모바일컴퓨터특강

VHDL 어휘 요소 (4) • 리터럴(Literal) • 일련의 수치 값을 표현 • 정수 리터럴 / 실수 리터럴로 구분 • 정수 리터럴: 소수점이 없는 10진수, (예) 20, 0, 146 • 실수 리터럴: 소수점을 갖는 10진수, (예) 23.1, 0.0, 3.14 • 진수 표기가 가능 – 2진수, 8진수, 10진수 • 표기법 –진수#수치데이터# • 예 –2진수 : 2#11011110# 8진수 : 8#0375# 16진수 : 16#FD# • 밑줄(‘_’) 문자 사용 가능 • 긴 숫자 데이터를 읽기 쉽게 작성 • 예 –123_456, 3.141_592_6, 2#1111_0101_1100_0000# 모바일컴퓨터특강

VHDL 어휘 요소 (5) • 문자(Characters) • 하나의 문자 데이터를 정의 • 단일 인용부호(single quotation) ‘‘를 사용 • 예 –‘A’, ‘z’, ‘2’, ‘,’, ‘-’, ‘ ‘ etc. • 문자열(Strings) • 2개 이상의 문자들로 구성된 문자 배열 • 이중 인용부호(double quotation) ““를 사용 • 예 –“A string”, “0001000”, etc. • 비트 문자열(Bit Strings) • 비트열을 2/8/16 진수 형태의 문자열로 표현 • 정의 형식 –”비트열”앞에 진수표시 문자(b/o/x)을 지정 • 예 –b”1111_0101_0000”, o”0375”, x”0d”, etc. 모바일컴퓨터특강

VHDL 어휘 요소 (6) • 특수 기호(Special Symbols) • 연산자 표기, VHDL 구문 표기 등의 목적으로 사용하는 문자 또는 문자열 • 1개 또는 2개의 문자로 구성 • 예 - +, -, *, /, =, =>, <=, :=, etc. 모바일컴퓨터특강

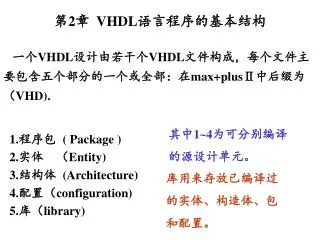

VHDL Design Description • VHDL design description은 설계하고자 하는 논리회로를 정의하는 entity와 architecture로 구성 • Entity • 하드웨어 외부입출력 인터페이스를 정의 • 하드웨어 블록의 이름과 입출력 PORT를 선언 • Architecture • 하드웨어의 내부를 표현 • 내부회로의 연결, 동작 또는 구조 등을 표현 모바일컴퓨터특강

BLACK_BOX rst q[7:0] d[7:0] co clk Entity Declarations (1) • 논리회로를 하나의 ‘Black Box’로 간주 • Entity는 논리회로를 정의하는 이름과 외부와의 인터페이스 신호(I/O Signal)을 정의 entity 논리회로이름is port( rst : in std_logic; … co : out std_logic); end 논리회로이름; 모바일컴퓨터특강

Entity Declarations (2) • 논리회로의 인터페이스 신호는 PORT 문장을 이용하여 정의 • 정의 형식: • 예 : port( rst : in std_logic; co : out std_logic ); PORT (signal_name : mode data_type); 모바일컴퓨터특강

Entity – Signal Mode • The port mode describes the direction in which data travels with respect to the component • in : data comes in this port and can only be read • out : data travels out this port • buffer : data may travel in either direction, but only one signal driver may be on at any one time • inout : data may travel in either direction with any number of active drivers allowed ; requires a Bus Resolution Function 모바일컴퓨터특강

Entity – Signal Type • 1 bit signal: bit, std_logic • 2 bit 이상의 signal: bit_vector, std_logic_vector • 2bit -- bit_vector(1 downto 0) std_logic_vector(1 downto 0) • 4bit -- bit_vector(0 to 3) std_logic_vector(0 to 3) • std_logic, std_logic_vector : IEEE 1164 Standard Signal Type으로 std_logic, std_logic_vector 이 사용될 때는 아래의 문장이 Entity문장 전에 미리 사용 되어야 함. Library ieee; Use ieee.std_logic_1164.all; 모바일컴퓨터특강

: ex_1 Entity 정의 예제 entity ex_1 is port ( A : in std_logic; B : inout std_logic; C : out std_logic; Y : buffer std_logic ); end ex_1; 모바일컴퓨터특강

Architecture Bodies (1) • 논리회로의 동작, 내부회로의 연결 또는 내부 구조 등을 묘사 • 두 부분으로 구성 : • 선언부 : 문장부에서 사용하는 신호, 변수, 상수 등을 정의하는 영역 • type declarations, signal declarations, component declarations, subprogram declarations • 병행문장부 : 논리회로의 내부 동작이나 구조를 묘사한 병행 문장을 포함하는 영역 • concurrent signal assignment statements, process statements, component instantiation statements 모바일컴퓨터특강

Architecture Bodies (2) • 기본 형식 : • 병행문장부 • begin과 end 사이에 서술된 문장들은 기본적으로 병행 수행 • 하드웨어 구현을 정의 • 동작적 표현(Behavioral Representation • 자료흐름적 표현(Dataflow Representation) • 구조적 표현(Structural Representation) • 혼합적 표현(Mixed Representation) architecture 아키텍처_이름of 엔티티_이름is {선언부} begin {병행문} end 아키텍처_이름; 모바일컴퓨터특강

Entity / Architecture 구성 LIBRARY __library_name; USE __library_name.__package_name.ALL; ENTITY __entity_name IS PORT( __input_name, __input_name : IN STD_LOGIC; __input_vector_name : IN STD_LOGIC_VECTOR(__high DOWNTO __low); __bidir_name, __bidir_name : INOUT STD_LOGIC; __output_name, __output_name : OUT STD_LOGIC ); END __entity_name; ARCHITECTURE a OF __entity_name IS SIGNAL __signal_name : STD_LOGIC; SIGNAL __signal_name : STD_LOGIC; BEGIN -- Process Statement -- Concurrent Procedure Call -- Concurrent Signal Assignment -- Conditional Signal Assignment -- Selected Signal Assignment -- Component Instantiation Statement -- Generate Statement END a; 모바일컴퓨터특강

Simple VHDL Code : AND Gate Library ieee;Use ieee.std_logic_1164.all; Entity and_2 is port( a, b : in std_logic; y : out std_logic );end and_2; Architecture dataflow of and_2 isbegin y <= a and b;end dataflow; Signal Type으로 std_logic이 사용될 때는 항상 사용. Entity 문장 : 입력 a,b, 출력 y를 나타냄 Architecture Body : 회로의 설명 모바일컴퓨터특강

객체(Object) • VHDL에서 값을 가질 수 있는 객체는 3가지 종류 • 신호(Signals) • 변수(Variables) • 상수(Constants) • The scope of an object is as follows : • Objects declared in a package are available to all VHDL descriptions that use package • Objects declared in an entity are available to all architecture associated with that entity • Objects declared in an architecture are available to all statements in that architecture • Objects declared in a process are available only within that process 모바일컴퓨터특강

객체(Object) - 신호 • VHDL 컴포넌트간의 연결에 사용되는 외적 변수 • 논리회로에서 구성 컴포넌트간을 연결하는 논리 신호(logic signal) 또는 선(wire)을 정의 • All VHDL signal assignments require either delta cycle or user-specified delay before new value is assumed • 신호는 일정 시간이 지난 시점에서 변한 값을 가진다 • 정의 형식 : • 사용 예: signal a, b, c : std_logic; a <= ‘1’; b <= ‘0’; c <= a and b; SIGNAL signal_name : type_name [ :=value]; 신호 할당 연산자 : 오른쪽에 있는 값을 왼쪽의 시그널에 대입 모바일컴퓨터특강

객체(Object) –신호 초기화 • 신호는 신호 선언 시에 초기화할 수 있다 • 신호의 초기화에서는 값을 바로 대입하므로 ‘<=‘연산자 대신에 ‘:=‘연산자를 사용한다 • 사용 예 : signal S : integer := 1; signal ONE_state : std_logic := ‘1’; signal Tmp : std_logic_vector(3 downto 0) := “1010”; 모바일컴퓨터특강

객체(Object) –신호 사용 예 Library ieee; Use ieee.std_logic_1164.all; Entity div_logic is port ( A, B, C : in std_logic; Y : out std_logic ); End div_logic; Architecture dataflow of div_logic is signal aorb : std_logic; signal ONE_state : std_logic := ‘1’; Begin aorb <= A or B; Y <= aorb and C and ONE_state; End dataflow; 모바일컴퓨터특강

객체(Object) - 변수 • 계산 결과를 임시로 저장하는 역할을 수행 • Provide convenient mechanism for local storage • 프로세스문 또는 부프로그램 내에서만 유효한 내적 변수 • 변수에 대한 할당연산은 즉시 실행되어 변수에 값이 바로 대입된다 • 정의 형식 : • 사용 예 : variable a, b : std_logic; variable s : integer; a := ‘1’; b := ‘0’; s := 1; VARIABLE variable_name : type_name [ :=value]; 변수 할당 연산자 : 오른쪽에 있는 값을 왼쪽의 변수에 대입 모바일컴퓨터특강

객체(Object) –변수 사용 예 모바일컴퓨터특강

객체(Object) - 상수 • 초기된 후에 값이 변하지 않는 데이터 객체 • Allow for easy update and readability • 정의 형식 : • 사용 예 : constant bits3_0 : std_logic_vector(2 downto 0) := "000"; signal y : std_logic_vector(2 downto_0); y <= bits3_0; CONSTANT constant_name : type_name [ :=value]; 모바일컴퓨터특강

객체(Object) –상수 사용 예 Even/Odd Bit Masking 모바일컴퓨터특강

자료형(Data Type) • Scalar Types • 열거형(Enumeration Type) • IEEE 1164 표준 자료형 • 부울형(Boolean Type) • 정수형(Integer Type) • 부동소수점형(Floating Type) • Composition Type • 배열형(Array Type) • 레코드형(Record Type) 모바일컴퓨터특강

열거형 자료형 선언 사용자 정의 자료형 선언 자료형 선언 (1) • 자료형 선언 • 미리 정의된 자료형 이외의 자료형은 사용자가 별도로 선언하여 사용 • 자료형 선언 형식 : TYPE 자료형_이름 IS 자료형_명세; • 사용 예 : TYPE Bit_4 IS (‘0’, ‘1’, ‘X’, ‘Z’); SIGNAL A : Bit_4; TYPE Digit IS INTERGER RANGE 0 TO 7; SIGNAL S : Digit; A <= ‘Z’; S <= 4; 모바일컴퓨터특강

부자료형 선언 (2) • 부자료형 선언 • 부자료형은 기본 자료형의 부분집합을 정의 • 부자료형 선언 형식 : SUBTYPE 부자료형_이름 IS 기본자료형_범위; • 사용 예 : SUBTYPE BYTE IS STD_LOGIC_VECTOR(7 DOWNTO 0); SUBTYPE WORD IS STD_LOGIC_VECTOR(15 DOWNTO 0); TYPE ANY_NUMBER IS INTEGER RANGE 0 to 1023; SUBTYPE PART_NUMBER IS ANY_NUMBER RANGE 0 TO 15; 모바일컴퓨터특강

Data Type - Scalar Types(1) • 열거형(Enumeration Type) • 객체가 가질 수 있는 값을 열거하여 새로운 자료형을 정의 • 사용 예 : TYPE State_type IS (stateA, stateB, stateC); TYPE Bit_2 IS (‘0’, ‘1’); TYPE Bit_3 IS (‘0’, ‘1’, ‘Z’); TYPE Bit_4 IS (‘0’, ‘1’, ‘Z’, ‘X’); signal X : Bit_3; signal Y : State_type; X < = ‘Z’; Y <= stateC; 모바일컴퓨터특강

Data Type - Scalar Types(2) • IEEE 1164 Standard Data Types • IEEE Library의 std_logic_1164 패키지에서 선언 • 자료형 종류 : • BIT / BIT_VECTOR • STD_LOGIC / STD_LOGIC_VECTOR • STD_ULOGIC • SIGNED / UNSIGNED • BIT / BIT_VECTOR • 논리 0 인 ‘0’과 논리 1 인 ‘1’의 값만 가지는 자료형 • 고임피던스(high impedance) 상태 등을 표현할 수 없어 현재는 거의 사용하지 않음 • BIT_VECTOR – BIT의 배열형 • VHDL 표준 IEEE 1076에 미리 정의되어 있음 모바일컴퓨터특강

Data Type - Scalar Types(3) • STD_LOGIC / STD_LOGIC_VECTOR • IEEE 1164 라이브러리에서 정의된 자료형으로 BIT 자료형 보다 융통성이 높은 자료형 • 정의된 값 : • ‘0’ : Strong Logic 0 / ‘1’ : Strong Logic 1 • ‘L’ : Weak Logic 0 / ‘H’ : Weak Logic 1 • ‘Z’ : High Impedance • ‘X’ : Strong Unknown / ‘W’ : Weak Unknown • ‘U’ : Uninitialized / ‘-’ : Don’t Care • STD_LOGIC_VECTOR – STD_LOGIC 자료형의 배열형 • std_logic_vector(0 to 10) – 오름차순 배열형 정의 • std_logic_vector(10 downto 0) – 내림차순 배열형 정의 모바일컴퓨터특강

C(1)=‘0’, C(2)=‘1’, …,C(4)=‘1’ Byte(7)=‘1’, Byte(6)=‘0’, …,Byte(0)=‘0’ Data Type - Scalar Types(4) • STD_LOGIC / STD_LOGIC_VECTOR • 사용 예: 모바일컴퓨터특강

Data Type - Scalar Types(5) • STD_ULOGIC • type std_ulogic is (‘U’, ‘X’, ‘0’, ‘1’, ‘Z’, ‘W’, ‘L’, ‘H’, ‘-’); • type std_logic is resolved std_ulogic; • SIGNED / UNSIGNED • SIGNED 자료형 : 부호있는 수 연산에 사용 • UNSIGNED 자료형 : 부호없는 수 연산에 사용 • 사용 패키지 : ieee 라이브러리의 std_logic_arith 패키지 모바일컴퓨터특강

Data Type - Scalar Types(6) • 부울형(Boolean Types) • 참(TRUE)과 거짓(FALSE)의 논리값을 가지는 자료형 • TRUE : 1, FALSE : 0 • 사용 예: TYPE BOOLEAN IS (false, true); signal flag : BOOLEAN; • 정수형(Integer Type) • 32 비트 크기의 정수를 표현 • -231 ~ +(231-1) = -2147483648 ~ + 2147483947 • 음의 정수는 2의 보수로 표현 • 산술 연산자를 이용하여 산술 연산에 적용 모바일컴퓨터특강

Data Type - Scalar Types(7) • 정수형(Integer Type) (계속) • “RANGE~TO~” 지정어를 사용하여 작은 크기의 정수형을 정의 • 사용 예: variable COUNT : INTEGER RANGE 0 TO 19; signal S : INTEGER; -- 32-bit integer number signal X : INTEGER RANGE -128 TO 127; -- signed 8-bit number signal D : INTEGER RANGE 0 TO 15; -- 4-bit umber • 부동소숫점형(Floating Type) • Minimum range for any implementation as defined by standard : -1.0E38 to 1.0E38 모바일컴퓨터특강

Data Type-Composition Type (1) • 배열형(Array Type) • 순서화된 데이터들의 집합을 정의 • 배열 내의 모든 요소들은 같은 자료형을 가지며, 순서가 정해져 있다 • 제한적 배열 : 배열의 크기를 설정할 수 있는 배열 • 1차원 배열 TYPE Word IS array(15 downto 0) OF std_logic; TYPE Byte IS array(7 downto 0) OF std_logic; TYPE Mem IS array(1023 downto 0) OF std_logic; signal X : Byte • 2 차원 배열 TYPE Mem IS array(0 to 1023) of std_logic_vector(15 downto 0); signal A : Mem; 모바일컴퓨터특강

Data Type-Composition Type (2) • 배열형(Array Type) • 무제한적 배열 : 배열의 크기를 지정하지 않은, 미리 정의되어 있는 배열 • 예 : TYPE BIT_VECTOR IS ARRAY(natural range <>) OF BIT; TYPE STD_LOGIC_VECTOR IS ARRAY(natural range <>) OF STD_LOGIC; • 무제한적 배열에 대해 배열의 크기를 지정하기 위해서는 부자료형을 정의하여 사용 TYPE BIT_VECTOR IS ARRAY(natural range <>) OF BIT; SUBTYPE low_part IS (BIT_VECTOR range 0 to 7); SUBTYPE high_part IS (BIT_VECTOR range 8 to 15); 모바일컴퓨터특강

Data Type Conversion • 자료형 변환 • 신호들이 서로 다른 자료형을 갖는 경우에 신호들간의 데이터 할당 또는 연산을 허용되지 않는다 • 자료형이 혼용되었을 때에 자료형 변환 함수를 사용 • CONV_INTEGER • CONV_UNSIGNED • CONV_SIGNED • CONV_STD_LOGIC_VECTOR • 자료형 변환 함수는 std_logic_arith 패키지에서 정의 • 사용 예: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; signal A, B : unsigned(7 downto 0); signal X, Y : integer; signal Z : std_logic_vector(7 downto 0); Y <= conv_integer(A + B); Z <= conv_std_logic_vector(X, 8); 모바일컴퓨터특강

속성(Attribute) (1) • 속성은 신호에 대한 동작이나 상태를 표현하는 특성 • 속성 접근 형식 : 신호_이름’속성_이름 • 미리 정의된 속성(Predefined Attributes) • low, high, left, right, pos, val, succ, pred ... • X’EVENT -- TRUE when there is an event on signal X • X’LAST_VALUE -- returns the previous value of signal X • Y’HIGH -- returns the highest value in the range of Y • X’STABLE(t) -- TRUE when no event has occurred on signal X in the past ‘t’ time • 사용자 정의 속성(User-defined Attributes) • 사용자가 필요에 따라 정의하여 사용하는 속성 모바일컴퓨터특강

속성(Attribute) (2) • ‘event’ 속성 • 논리회로에서 가장 많이 사용하는 속성 • 클럭 신호의 에지 상태(rising edge/falling edge)에 따라 동작을 지정하는 경우에 사용 • 사용 예: 모바일컴퓨터특강

연산자(Operators) (1) • Relational operators • Logic and relational operators precedence = /= < <= > >= Highest not = /= < <= > >= and or nand nor xor xnor Lowest 모바일컴퓨터특강

연산자(Operators) (2) compare a = bc Incorrect … when a = b and c else … equivalent to … when (a = b) and c else … Correct … when a = (b and c) else … 모바일컴퓨터특강

연산자(Operators) (3) 모바일컴퓨터특강

문장(Statements) (1) • 병행 문장(Concurrent Statements) • Signal Assignment, Simple • Signal Assignment, Conditional • Signal Assignment, Selected • Process Statement • 순차 문장(Sequential Statements) • Wait Statement • If Statement • Case Statement • For Loop Statement 모바일컴퓨터특강

문장(Statements) (2) • 디지털 논리회로 내의 모든 요소들은 항상 병행적으로 동작하므로 병행문장을 사용하여 표현 • 일반 프로그램 언어와 같이 논리회로의 동작을 알고리즘 방식으로 정의하기 위해 순차문장을 사용 모바일컴퓨터특강

y <= b; (1) b에 변화가 생길 때마다 b의 값이 y에 출력됨 (2) Sensitivity List : b y <= a or b; (1) a 나 b에 변화가 생길 때마다 a or b의 값이 y에 출력됨. (2) Sensitivity List : a,b Concurrent Statements - Signal Assignment, Simple signal_name <= expression; 모바일컴퓨터특강