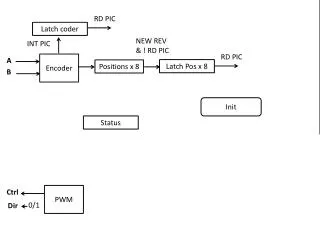

Encoder, Tristate Driver

Encoder, Tristate Driver. Outline. Review: demo decoder FPGA example Encoder Demo Encoder, problems Encoder using for loop Priority Decoder Application of Priority Decoder Tristate Buffer Implementation of a MUX using Tri-state buffer. Definition of an Encoder. 2 n input lines

Encoder, Tristate Driver

E N D

Presentation Transcript

Outline • Review: demo decoder FPGA example • Encoder • Demo Encoder, problems • Encoder using for loop • Priority Decoder • Application of Priority Decoder • Tristate Buffer • Implementation of a MUX using Tri-state buffer

Definition of an Encoder • 2n input lines • n output lines • Performs the inverse operation of a decoder

Implementation of an Encoder • Focus on one output at a time x=D4+D5+D6+D7

Implementation of an Encoder • Focus on one output at a time y=D2+D3+D6+D7

Implementation of an Encoder • Focus on one output at a time z=D1+D3+D5+D7

Uncertainty of an Encoder • What if all the input lines are 0? • Use a valid bit • What if more than one input line are high? • Use priority—certain bits are more important than other bits

encode83a.v Check 0000000 is present.

encode83a_top.v Turn off the decimal bit if the input is not valid

Demonstrate encode83a.v • Input: 00000000 (decimal bit is off) • Intput:00000010 (Get 001) • Intput:00000011 (Still get 001)

Priority Encoder Not a Valid State

Write a for loop to Implement encoder. typo, should be a[i] as opposed to x[i]. y will be set to I if ith bit of a is a 1.

Three State Gate • Possible state: • 1, 0, high impedance state! • High impedance: • The output appears disconnected from the input

Application of Tri-State Gate You can not make a connection like this Unless you use a tri-state device!