FPGA basics and Nios II Processor Intro

280 likes | 582 Vues

FPGA basics and Nios II Processor Intro. Week 2 Dr. Kimberly E. Newman Hybrid Embedded Systems. Material Covered. Textbook Chapter 5 Nios II Processor Reference Handbook Chapter 1 & 2 Homework Assignment #1 is available. Assignment is due next week before class.

FPGA basics and Nios II Processor Intro

E N D

Presentation Transcript

FPGA basics and Nios II Processor Intro Week 2 Dr. Kimberly E. Newman Hybrid Embedded Systems

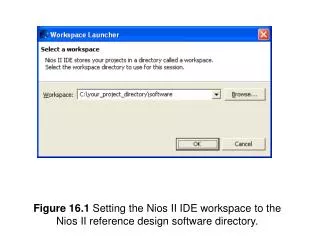

Material Covered • Textbook Chapter 5 • Nios II Processor Reference Handbook • Chapter 1 & 2 • Homework Assignment #1 is available. • Assignment is due next week before class. • Submit through Blackboard since there will be code involved that needs to be verified. • Turn in signed verification sheets for Lab #1 to Dan for recording in Blackboard. • Lab #2 will cover the LCD peripheral and interfacing to external memory (SDRAM).

Field Programmable Devices • The fundamental piece of a configurable logic device is a programmable macrocell. • Figure 5.20 on page 213 shows an overview of the components in a simple configuration. • Each macrocell has a programmable register that an be either a D, T, JK and SR flip-flop with individual clear and clock control. • Input to the macrocell is configured through the logic array. • Eight product terms form a programmable AND array that feeds an OR gate for combinatorial logic implementation. And XOR gate is provided to allow for inversion of the output. • Routing and use of clocks and output signals are also controlled through configuration.

Complex Programmable Logic Devices (CPLD) • Multiple PLDs are placed in a single device as shown on page 214 in fig 5.21. • Typically the CPLD has an EEPROM included so that the configuration is not lost when power is removed. • Look at the Data Sheet for the MAX II http://www.altera.com/literature/hb/max2/max2_mii51002.pdf

Logic Array Blocks (LAB) • Each LAB consists of 10 LEs, LE carry chains, LAB control signals, a local interconnect, a look-up table (LUT) chain, and register chain connection lines. • There are 26 possible unique inputs into a LAB with an additional 10 local feedback input lines fed by LE outputs in the same LAB

Field Programmable Gate Arrays(textbook section 5.4) • An FPGA is more flexible than a CPLD. • The logic blocks in an FPGA are connected by wiring channels that are much smaller than those of a CPLD. • There are many more logic blocks available in the FPGA. • Memory blocks are also available that can be configured as general purpose RAM.

Flex 10k • SRAM-based that can be programmed through the JTAG interface • A serial PROM can be used to provide configuration information on power up • The EPF10K70 has a total of 70,000 typical gates that include logic and RAM. • The entire array contains 468 Logic Array Blocks (LABs) arranged into 52 columns and 9 rows.

Altera’s Cyclone FPGA (pg 223 ) • This processor is based on a 1.5 V, 0.13µm all-layer copper SRAM process. • Densities can reach up to 20,060 logic elements and up to 288 Kbits of RAM. • The devices supports the creation of phase-lock-loops (PLLs) for clocking and a dedicated double data rate (DDR) interface to meet DDR SDRAM and fast cycle RAM (FCRAM) memory requirements. • We are using the EP2c35F672C6N with the DE2 board.

Nios II Processor System basics (info from the PRH) • General purpose RISC processor core • Full 32-bit instruction set, data path, and address space • 32 general-purpose registers • 32 external interrupt sources • ALU supports: • Single-instruction 32x32 multiply and divide producing a 32-bit result (Dedicated instructions for computing 64-bit and 128-bit products of multiplication) • Floating-point instructions for single-precision floating-point operations • Single Instruction barrel shifter • I/O capabilities: • Access to on-chip peripherals • Interfaces to off-chip memories and peripherals

Nios II Processor System basics • Debugging capabilities: • Hardware-assisted debug module enabling processor start, stop, step, and trace under integrated development environment (IDE) control • SignalTap II Embedded Logic Analyzer • Optional features • Memory Management Unit (MMU) • Memory Protection Unit (MPU) • Speed • Performance up to 250 DMIPS

Customizing Nios II Processor Designs • Pin locations on the FPGA layout can be moved to make traces smaller for external access to the processor. • Glue logic on the FPGA can be implemented. • On the larger Altera devices the Nios II processor system consumes on the order of 5% of the on board resources. • Additional cores and peripherals can be included in a design to enhance the system performance

Processor Architecture • Nios II architecture describes an instruction set architecture (ISA). The ISA in turn necessitates a set of functional units that implement the instructions. • A Nios II processor core is a hardware design that implements the Nios II instruction set and supports the functional units described in this document. • The processor core does not include peripherals or the connection logic to the outside world.

Nios II Processor Core Block Diagram • Functional Units: • Register file • Arithmetic logic unit (ALU) • Interface to custom instruction logic • Exception controller • Interrupt controller • Instruction bus • Data bus • Memory management unit (MMU) • Memory protection unit (MPU) • Instruction and data cache memories • Tightly-coupled memory interfaces for instructions and data • JTAG debug module

Register File • Nios II architecture supports a flat register file • There are thirty two 32-bit general-purpose integer registers • Up to thirty two 32-bit control registers with supervisor and user modes to allow system code to protect control registers from errant applications. • Allows for the future additional of floating-point registers

Arithmetic Logic Unit • Operates on data stored in general-purpose registers • Operations take one or two inputs from registers and stores a result back in a register.

Instructions • Unimplemented Instructions • Some core implementations do not provide support for the entire instruction set. • An exception is generated so that the instruction can be emulated in software. • To determine a list of potentially unimplemented instructions refer to the Programming Model chapter of the Nios II Processor Reference Handbook • Custom Instructions • User-defined custom instructions are allowed. The ALU connects directly to the new instruction logic so that use and access are the same as the native instructions. • For further information refer to the Nios II Custom Instruction User Guide

Floating Point operations • Single precision floating point is supported as specified in the IEEE Std 754-1985

Tradeoffs • Floating point operations do require many more elements in the FPGA. • Designers should be aware of tradeoffs in the HW/SW implementation. • Speed vs. resource usage should be evaluated for a given application.

Motivational Videos: • Hybrid embedded systems are growing in need and facilitate the grand challenges of tomorrow. • Transportation, environmental management and health care applications are just a few examples of where better designs are needed. Autonomous Vehicles Big Belly Robot Garbage Bin Robonurse