Modern Crossbar Switch Designs for Multiprocessing Systems on Chip and Multicore Architectures

This document explores the hardware design of several contemporary crossbar switches utilized in multiprocessing systems on chip (MPSoC) and multicore designs. It covers various architectures, including AMD Opteron and Intel Xeon 7500, emphasizing their buffering techniques, bandwidth capabilities, and crosspoint implementations. Key characteristics such as system request queues, buffer sizes, and pipelining are compared among different architectures. Issues like output congestion and solutions, including the Knockout switch and concentrator designs, are also discussed in detail.

Modern Crossbar Switch Designs for Multiprocessing Systems on Chip and Multicore Architectures

E N D

Presentation Transcript

Crossbar switches By Alejandro Ayala

Hardware design • Show hardware design of several modern crossbar switches used for multiprocessing system on chip or multicore design.

AMD Opteron Architecture [1] • Integrated N.Bridge • Data & Command packets are separated

Intel Xeon 7500 (cont) • 8 port (each 80bit) • Intel QuickPath Interconnect communication

UltraSPARC T2 [4] • pipeline crossbar • High-bandwidth • 8x9 xBar • Cores-Mem • Cores-I/O

UltraSparc T2 (cont) • Divided into two parts • PCX • CPX • PCX/CPX divided into two parts • Arbiter • Assigns by old age • Data slice

Characteristics of the crossbar • Compare characteristics of several switches used in modern MPSoC design • Are the switches buffered or bufferless? Is buffering done at the input, output, or at each crosspoint? What is the size of the buffers? Why that much? • How is the crosspoint implemented? Are the crossbars pipelined? What is the size of the crossbar switch? What is the bandwidth?

AMD Opteron [1] • Buffers at Input • Size are allocated to optimize throughput

System Request Queue (SRQ) • What is the System request queue in AMD64 Opteron, Athlon X2?

System Request Queue [1] • Prioritizes the access from both cores to use the crossbar. • Prevents contention to memory/resources

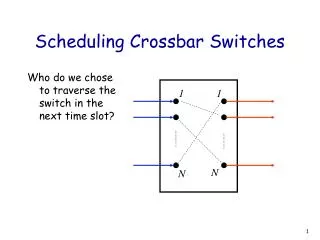

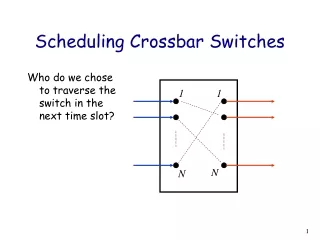

Knockout switch • What is knockout switch?

Knockout switch [3] • Problem: • Fully connected switch (ie every input connects to every output) • Congestion at output – different input might want to talk to same output. • Solution: • Concentrator at output • Buffer

Knockout switch Bus Interface

References [1] Pat Conway, Bill Hughes, "The AMD Opteron Northbridge Architecture," IEEE Micro, vol. 27, no. 2, pp. 10-21, Mar./Apr. 2007,doi:10.1109/MM.2007.43 [2] Intel Xeon Processor 7500 series Volume 2, Datasheet, March 2010 [3] Y. Yeh, M. Hluchyj, and A. Acampora, “The Knockout Switch: A Simple, Modular Architecture for High-Performance Packet Switching,” IEEE J. Selected Areas in Comm., vol. 5, no. 8, pp. 1274- 1287, Oct. 1987. [4] U. G. Nawathe, et al.. “An 8-Core 64 Thread 64b Power-Efficient SPARC SoC,” in IEEE International Solid-State Circuits Conference (ISSCC), Dig. Tech Papers, Feb. 2007, pp. 108-110.