REDUCED POWER SHIFT REGISTER WITH MULTIPHASE CLOCKS

200 likes | 424 Vues

REDUCED POWER SHIFT REGISTER WITH MULTIPHASE CLOCKS. ELEC 6270 Kannan Govindasamy. OUTLINE. Objective Simulation Specification Background information Implementation Results Conclusion. OBJECTIVE. Design and Verify a 32 bit Shift Register with Multi-phase Clocks

REDUCED POWER SHIFT REGISTER WITH MULTIPHASE CLOCKS

E N D

Presentation Transcript

REDUCED POWER SHIFT REGISTER WITH MULTIPHASE CLOCKS ELEC 6270 Kannan Govindasamy

OUTLINE • Objective • Simulation Specification • Background information • Implementation • Results • Conclusion

OBJECTIVE • Design and Verify a 32 bit Shift Register with Multi-phase Clocks • Study Low Voltage Power and Delay characteristics

Dynamic Signal transitions Logic activity Glitches Short-circuit Static Leakage Background Information

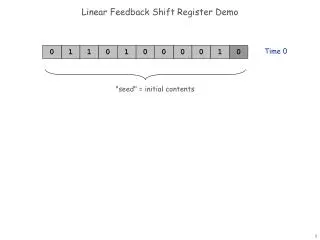

Multiphase Clock Generators Modified Johnson counter is used for Multiphase Clock generation

Summary • A power reduction of 39.1% is achieved when degree of parallelism is 4. • A power reduction of 45.07% is achieved for N=8. for further parallelism power reduction gets stabilized

Reference • ELEC 6270 class slides by Dr.Agrawal • Tsung-chu Huang, Kuen-Jong Lee, A Low-Power LFSR Architecture, Test symposium 2001