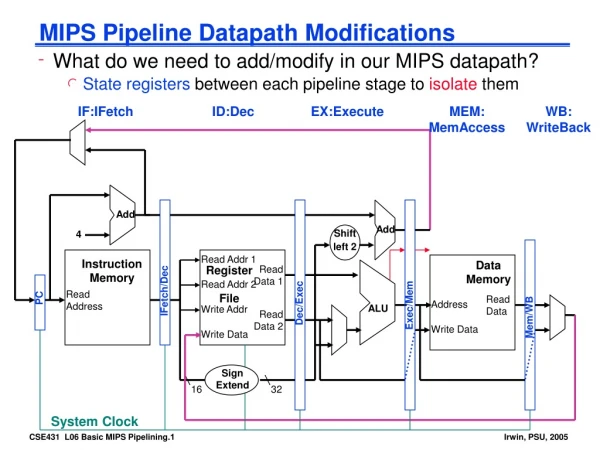

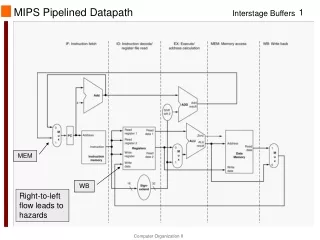

MIPS Datapath

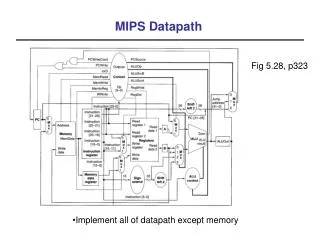

MIPS Datapath. Fig 5.28, p323. Implement all of datapath except memory. Control Sequence. Fig 5.38, p339 You will change these signals in your testbench for this lab Ignore MemRead and MemWrite. Tasks in a Testbench. task ctrl_if; output PCWrite, ALUrc… begin ALUSrcA = 0; IorD = 0;

MIPS Datapath

E N D

Presentation Transcript

MIPS Datapath Fig 5.28, p323 • Implement all of datapath except memory

Control Sequence • Fig 5.38, p339 • You will change these signals in your testbench for this lab • Ignore MemRead and MemWrite

Tasks in a Testbench task ctrl_if; output PCWrite, ALUrc… begin ALUSrcA = 0; IorD = 0; IRWrite = 1; ALUSrcB = 01; ALUOp = 00; // special PCWrite = 1; PCSource = 00; end endtask task ctrl_id; output ALUSrcA, ALUSrcB … begin ALUSrcA = 0; ALUSrcB = 11; ALUOp = 00; // special end endtask • Mask a task for every control state • ctrl_if, ctrl_id, ctrl_ex_mem, ctrl_ex_r, ctrl_ex_b, ctrl_ex_j, … • ALUOp must be replaced with 4-bit ALU control values

Instruction Control Sequences task cseq_add; input clk; output PCWriteCond, PCWrite, … begin @ (posedge clk) ctrl_if; @ (posedge clk) ctrl_id; @ (posedge clk) ctrl_ex_add; @ (posedge clk) ctrl_mem_add; end endtask • A clock-by-clock control sequence is defined • Each type of instruction can be modelled with a task • Need a clock which is 1 step earlier than regular clock

Issue Instructions • Issue an instruction by applying the instruction and then calling the task to generate the control sequence intial begin @(posedge sclk) MemDataIn = 000000|00010|00001|00000|00000|000000; cseq_add(sclk); end op rs rt rd shamt funct • Op, shamt, and funct do not matter

Initializing Registers • You will need to initialize registers to perform tests • Use addi instruction intial begin @(posedge sclk) reset = 1; @(posedge sclk) reset = 0; MemDataIn = 000000|00000|00001|0000000011111111; cseq_addi(sclk); end op rs rt immediate • This initializes register $1 to 255

Observing Registers • You will need to observe registers to check test results • Make a new regobs instruction intial begin @(posedge sclk) MemDataIn = 000000|00000|00000|00001|000111|11111; cseq_regobs(sclk); end op rs rt rd shamt funct • This puts rs (rt) contents into register A(B) for observation