Finite State Machines for Digital Logic Applications

E N D

Presentation Transcript

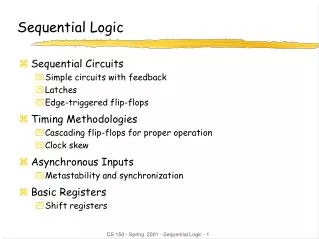

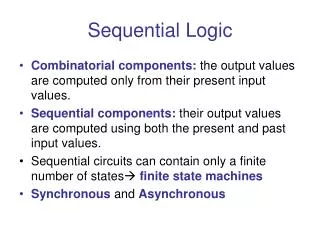

Sequential Logic • The combinational logic circuits we have been studying have no memory. The outputs always follow the inputs. • There is a need for circuits with a memory, which behave differently depending upon their previous state. • An example is the vending machine, which must remember how many and what kinds of coins have been inserted, and which behave according to not only the current coin inserted, but also upon how many and what kind of coins have been deposited previously. • These are referred to as finite state machines, because they can have at most a finite number of states. D = 0 D = 1 Q=0 Q=1 D = 0 D = 1

(Synchronous) Finite State Machine (FSM): FSM clu Theory State elem Digital Techniques Fall 2007 André Deutz, Leiden University

Finite State Machine (FSM) • A finite state machineis s digital device having: • A finite set of States: S1, S2, …, Sk (where k is the number of states, optionally one of this is distinguished as the initial state) • A finite number of binary Inputs I1, …, Im(where m is the number of inputs) • A finite number of binary Outputs O1, …, On (where n is the number of outputs) • A set of State Transition Rulesrules, specifying for each choice of current state Ss and input values I1, …, Im a next state Ss’ and • A set of output rules specifying for each choice of the current Ss and input values I1, …, Imthe binary value at each output Digital Techniques Fall 2007 André Deutz, Leiden University

Finite State Machine (FSM) • In a Moore machinethe FSM’s outputs are functions of the current state alone • The behavior of such a system can be specified by giving rules for making transitions between states and the set of output values corresponding to each state • The alternative model, called a Mealy machine, allows outputs to reflect current inputs as well as current state. • Most abstract representation of FSMs is a state-transition diagram Digital Techniques Fall 2007 André Deutz, Leiden University

(Synchronous) Finite State Machines m n inputs outputs Combinational Circuit k k Storage Elements Next state Present state feed-back loop Clock - Acyclic graph - static discipline - Can exhaustively be enumerated by 2k+m rows And k+n columns - Engineered cycles - Works only if dynamic discipline obeyed - Remembers k bits for a total of 2k unique combinations combinations Digital Techniques Fall 2007 André Deutz, Leiden University

Finite State Machine, in short: i f o o . . . . . . O u t p u t s . . . I n p u t s i C o m b i n a t i o n a l f k m l o g i c u n i t An FSM is composed of a combinational logic unit and delay elements (called flip-flops) in a feedback path, which maintains state information. . . . S t a t e b i t s Q D 0 0 s 0 . . . Q D n n s n S y n c h r o n i z a t i o n s i g n a l D e l a y e l e m e n t s ( o n e p e r s t a t e b i t )

The state of a sequential circuit is a collection of state variables whose values at any one time contain all the information about the past necessary to account for the circuit’s future behavior Herbert Hellerman, Digital Computer Systems Principles, McGraw Hill, 1967, p237 Digital Techniques Fall 2007 André Deutz, Leiden University

Finite State Machine Design • Counter has a clock input, CLK, and a RESET input. • Has two output lines, which must take values of 00, 01, 10, and 11 on subsequent clock cycles. A Modulo-4 Counter T i m e ( t ) 4 3 2 1 0 4 3 2 1 0 T i m e ( t ) q R E S E T 0 0 0 0 1 0 1 1 0 0 0 q 0 1 0 1 0 2-bit 3 - b i t 1 s y n c h r o n o u s s D Q 0 c o u n t e r s 0 s D Q It requires two flip-flops to store the state. 1 Q s 1 Q C L K

State Transition Diagram for Mod-4 Counter Digital Techniques Fall 2007 André Deutz, Leiden University

Next State O u t p u t 0 0 O u t p u t 0 1 s t a t e s t a t e Present State RESET 0 1 A B/01 A/00 B C/10 A/00 C D/11 A/00 D A/00 A/00 0 / 0 1 R E S E T 0 1 / 1 State Table A B 1 / 0 0 1 0 / 1 q q 1 / 0 0 1 0 1 / 0 0 0 / 1 0 0 / 0 0 1 / 0 0 Present State RESET 0 1 A:00 01 00 B:01 10 00 C:10 11 00 D:11 00 00 State Table With States Assigned C D 0 / 1 1 O u t p u t 1 0 O u t p u t 1 1 s t a t e s t a t e State Transition Diagram for a Modulo-4 Counter • The state diagram and state table tell “all there is to know” about the FSM, and are the basis for a provably correct design.

Valid State Transition Diagrams Arcs leaving a state must be: (1) mutually exclusive – can’t have two choices for a given input value (2) collectively exhaustive – every state must specify what happens for each possible input combination. “Nothing happens”means arc back to itself. Digital Techniques Fall 2007 André Deutz, Leiden University

Truth Table • Develop equations from this truth table for s0(t+1), s1(t+1),q0(t+1), and q1(t+1) from inputs r(t), s0(t) and s1(t)

Equations Implement these equations

Logic Design for a Modulo(4) Counter There are many simpler techniques for implementing counters.

Sequence Detectors • A sequence detector is a special kind of sequential circuit that looks for a special bit pattern in some input. • The recognizer circuit has only one input, X. • One bit of input is supplied on every clock cycle. For example, it would take 20 cycles to scan a 20-bit input. • This is an easy way to permit arbitrarily long input sequences. • There is one output, Z, which is 1 when the desired pattern is found. • Our example will detect whether the last 3 inputs contain exactly 2 ones: • Input X: … 011011100… • Output Z: …001111010 … • Here, one input and one output bit appear every clock cycle. • This requires a sequential circuit because the circuit has to “remember” the inputs from previous clock cycles, in order to determine whether or not a match was found. Digital Techniques Fall 2007 André Deutz, Leiden University

A Sequence Detector • Design a machine that outputs a 1 when exactly 2 of the last 3 inputs are 1. • e.g. input sequence of 011011100 produces an output sequence of 001111010 • Assume input is a 1-bit serial line. • Use D flip-flops and 8-1 multiplexers. • Begin by constructing a state transition diagram.

Sequence Detector State Transition Diagram D is the state of having read the most recent two bits as 00 • • Design a machine that outputs a 1 when exactly two of the last three inputs are 1. E is the state of having read the most recent two bits as 01 F is the state of having read the most recent two bits as 10 G is the state of having read the most recent two bits as 11 Digital Techniques Fall 2007 André Deutz, Leiden University

Takes care of first or of first two inputs; some- Times you have no more Than 2 inputs Sequence Detector State Transition Diagram D is the state of having read the most recent two bits as 00 • • Design a machine that outputs a 1 when exactly two of the last three inputs are 1. E is the state of having read the most recent two bits as 01 F is the state of having read the most recent two bits as 10 G is the state of having read the most recent two bits as 11 Digital Techniques Fall 2007 André Deutz, Leiden University

State Transition Diagram for Sequence Detector • Design a machine that outputs a 1 when exactly 2 of the last 3 inputs are 1. 0/0 0/0 D 1 / 0 B 0 / 0 0 / 0 E 1 / 0 0 / 0 1 / 1 A 0 / 0 F 1 / 1 1 / 0 C 0 / 1 G • Convert table to truth table (how?). • Solve for s2 s1 s0 and Z. 1 / 0 1 / 0 • Discuss: the “meaning” of each state.

0 0 0 0 x 0 0 0 x 0 0 0 0 0 0 0 x 0 0 1 x 0 0 1 x 0 0 1 0 0 0 1 1 0 1 0 x 0 1 0 x 0 1 0 0 0 1 0 D Q D Q D Q Z x 0 1 1 x 0 1 1 x 0 1 1 0 0 1 1 s s s 1 1 0 0 x 1 0 0 x 1 0 0 x 1 0 0 2 1 0 Q Q Q x 1 0 1 x 1 0 1 x 1 0 1 x 1 0 1 1 1 1 0 x 1 1 0 x 1 1 0 x 1 1 0 0 1 1 1 0 1 1 1 0 1 1 1 0 1 1 1 C L K Logic Diagram for Sequence Detector

A Vending Machine Controller • Accepts nickel, dime, and quarter. When value of money inserted equals or exceeds twenty cents, machine vends item and returns change if any, and waits for next transaction. • Implement with PLA and D flip-flops.

State Transition Diagram for Vending Machine Controller 1/0 = dispense / do not dispense merchandise 1/0 = return / do not return a nickel in charge A d i m e i s i n s e r t e d 1 / 0 = return / do not return a dime in change Q / 110 D / 110 N / 100 N / 000 D / 000 A B D 0 ¢ 5 ¢ 1 5 ¢ Q / 101 Q / 111 D / 000 N / 000 Q / 111 N / 000 N = Nickel D = Dime Q = Quarter D / 100 C 1 0 ¢

Truth Table for Vending Machine Controller D i s p e n s e R e t u r n n i c k e l P r e s e n t N e x t R e t u r n d i m e s t a t e s t a t e C o i n B a s e 1 0 s s x x s s z z z 1 0 1 0 1 0 2 1 0 e q u i v a l e n t 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 0 2 0 0 1 0 0 0 1 1 0 3 0 0 1 1 d d d d d 4 0 1 0 0 1 0 0 0 0 5 0 1 0 1 1 1 0 0 0 6 0 1 1 0 0 0 1 0 1 7 0 1 1 1 d d d d d 8 1 0 0 0 1 1 0 0 0 9 1 0 0 1 0 0 1 0 0 1 0 1 0 1 0 0 0 1 1 1 1 1 1 0 1 1 d d d d d 1 2 1 1 0 0 0 0 1 0 0 1 3 1 1 0 1 0 0 1 1 0 1 4 1 1 1 0 0 1 1 1 1 1 5 1 1 1 1 d d d d d

s s x x z x 1 0 1 0 2 1 z x 5 x 5 1 0 z P L A 0 Q D s 0 0 ( a ) C L K 1 Q D s 2 1 4 5 D i s p e n s e R e t u r n n i c k e l P r e s e n t N e x t R e t u r n d i m e 6 s t a t e s t a t e C o i n B a s e 1 0 s s x x s s z z z 1 0 1 0 1 0 2 1 0 e q u i v a l e n t 8 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 0 9 2 0 0 1 0 0 0 1 1 0 3 0 0 1 1 d d d d d 1 0 4 0 1 0 0 1 0 0 0 0 5 0 1 0 1 1 1 0 0 0 1 2 6 0 1 1 0 0 0 1 0 1 7 0 1 1 1 d d d d d 1 3 8 1 0 0 0 1 1 0 0 0 9 1 0 0 1 0 0 1 0 0 1 0 1 0 1 0 0 0 1 1 1 1 4 1 1 1 0 1 1 d d d d d 1 2 1 1 0 0 0 0 1 0 0 1 3 1 1 0 1 0 0 1 1 0 1 4 1 1 1 0 0 1 1 1 1 1 5 1 1 1 1 d d d d d s s z z z 1 0 2 1 0 ( c ) ( b ) (a)FSM Circuit, (b)Truth Table, and (c)PLA Realization for Vending Machine Controller

Moore Counter • Mealy Model: Outputs are functions of Inputs and Present State. • Previous FSM designs were Mealy Machines, in which next state was computed from present state and inputs. • Moore Model: Outputs are functions of Present State only.

0 0 0 x 0 1 4 - t o - 1 z D Q 0 M U X 1 0 1 s 0 1 1 Q 0 0 0 1 4 - t o - 1 z D Q M U X 1 1 0 s 1 1 1 Q Mealy versus Moore Machines • Moore model: Outputs are functions of present state only. • Mealy model: Outputs are functions of inputs and present state. • Previous FSM designs were Mealy machines, because next state was computed from present state and inputs. x z 2 1 z x 5 x 5 1 0 z P L A 0 Q D s 0 C L K C L K Q D s • Both are equally powerful. 1

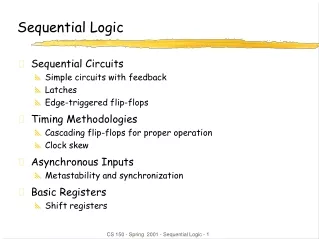

Summary of Design Procedure FSMs • Step 1: Given the problem statement, derive the state (transition) table: • The table should show inputs, present states, next states and outputs. • It may be easier to find a state diagram first, and then convert that to a table. • Step 2 (optional): Apply state-reduction methods to reduce (if possible) the number of states. • We will not discuss state-reduction methods in this course. • Step 3: Assign binary codes to the states in the state table, if you haven’t already. • If you have n states, your binary codes will have at least log2 n bits. • Step 4: Determine the number of Flip-Flops needed and the type of Flip-Flops to be used: • If you have n states, your circuit will have at least log2 n Flip-Flops. • The types of Flip-Flops may be given in the initial specification. If not, select the type according to some criteria, e.g., to get simpler circuit or to make the design procedure easier. Digital Techniques Fall 2007 André Deutz, Leiden University

Summary of Design Procedure FSMs • Step 5: For each flip-flop and each row of your state table, find the flip-flop input values that are needed to generate the next state from the present state: • You can use Flip-Flop excitation tables here. • Step 6: Derive the characteristic (Flip-Flop input) equations from the state table. • Step 7: Derive the primary output equations from the state table. • Step 8: Simplify the Flip-Flop input equations and output equations: • Use K-maps or • Other simplification methods • Step 9: Draw the logic diagram of the circuit. Digital Techniques Fall 2007 André Deutz, Leiden University

FSMs • They are here to stay • discussion Digital Techniques Fall 2007 André Deutz, Leiden University

From Mealy to Moore (1) 1 0 1/11 0/11 A /11 A 0 1 0/00 1/01 00 is accommodated by next state 01 is accommodated by next state Move output forward into the next State. If this results in a state with two different outputs, then split that state into as many states as there are different outputs. The next states From the created states are the same as the original ones Digital Techniques Fall 2007 André Deutz, Leiden University

From Mealy to Moore (2a) 0/1 0/0 B/0 A C/1 B A C 1/0 1/1 0/1 0/1 0 1/0 1 Digital Techniques Fall 2007 André Deutz, Leiden University

From Mealy to Moore (2b) 0/1 0 A A C/1 B/0 A C/1 B/0 1/0 1 Split state to accommodate different outputs. Destination from split states stays the same: 0/1 0/1 0 1 1/0 Digital Techniques Fall 2007 André Deutz, Leiden University

From Mealy to Moore (2c) 0/1 0 C/1 A1 /1 A2 /0 B/0 B/0 A A C/1 1 1/0 0 0 1 1 1 0 Digital Techniques Fall 2007 André Deutz, Leiden University

Programs are translated by other programs into different forms What happens when you enter: gcc –o hello hello.c? printf.o Pre- processor (cpp) Compiler (cc1) Assembler (as) Linker (ld) hello.c hello.i hello.s hello.o hello Source program (text) Assembly program (text) Modified source program (text) Relocatable object programs (binary) Executable object program (binary)

Remarks on Assembly Programming • We will consider the Assembly Language of Tiny Mips • The next slide summarizes the instruction set of TM; the slt, brlt and halt instructions will be considered as part of the repertoire as well • Remember as powerful as C++ (obviously not as expressive as C++) Digital Techniques Fall 2007 André Deutz, Leiden University

C++ to Assembly • How would you translate the following fragments of C++ into TM Assembly: int a, b; a = 4; b= 4; a = a – b; Digital Techniques Fall 2007 André Deutz, Leiden University

C++ to TM Assembly: selection 2) Assume a and b are fetched from memory and Stored in reg0 and reg1 respectively Set negation of condition (a < = b) (i.e.: test (b < a)) brlt address of beginning of ft true task br address of instruction after if-then-else false task 1) if (a < = b) { // true task (TT) } else { // false task (FT) }11 3) slt reg1, reg0 brlt “false task” true task br “end of if-then-else” false task Digital Techniques Fall 2007 André Deutz, Leiden University

C++ to TM Assembly: selection 2) pseudo ? 1) if (a < b) { // true task (TT) } else { // false task (FT) }11 3) assembly: ? Digital Techniques Fall 2007 André Deutz, Leiden University

C++ to TM Assembly: while 2) Pseudo assume reg0 is loaded with a and reg1 with b set negation of condition (a <= b) (i.e., set condition (b < a)) branch to end of while task branch “set condition” 1) while (a < = b) { // task } 3) assembly: slt reg1, reg0 brlt “end-of-while address” task update of reg0 (and/or) reg1 br “slt reg1, reg0 address” Digital Techniques Fall 2007 André Deutz, Leiden University

write a TM assembly program which computes the • maximum of two numbers • b) write a TM assembly program which computes the max • of three numbers • c) suppose the 0th memory location contains the number • of numbers (denoted by n). the next n memory locations • contain n numbers. write a TM assembly program which • computes the max of these n numbers Digital Techniques Fall 2007 André Deutz, Leiden University

Summary • Built an automatic information processing device (a la von Neumann) • As primitives: AND, OR, NOT, state elements (d-latches and d-flip-flops); all these can be implemented on a macroscopic level – relays, waterpipes, knex) • Combinational logic units (muxes, adders, ALUs) • Sequential circuits (most simple: d-latches and d-flip-flops; registers; memory; ) • Von Neumann model; eternal von Neumann fetch-decode-execute cycle • Datapath • Control • Other approaches: quantum computing, dna computing • Look also at the website of Great Principles of Computer Science (http://cs.gmu.edu/cne/pjd/GP/ )

Q (D-latch) data clock Time

D-latch ? Q data clock Time

D-flip-flop Rising edge ? Q D-latch ? Q data clock Time