Enhancing IC Design Education: The Q.U.I.L.T. GUI-Based Floorplanning Tool

Q.U.I.L.T. (Quick Utility for IC Layout and Temperature modeling) is a GUI-based environment designed to aid computer architecture research and education. Developed by researchers from the University of Rochester and Cornell University, this tool facilitates easier exploration of design trade-offs related to performance, cost, and power by simulating floorplans and estimating interconnect delays and thermal effects. Q.U.I.L.T. enhances student understanding through a more intuitive interface, allowing hands-on learning and supporting integration with established simulators like HotSpot.

Enhancing IC Design Education: The Q.U.I.L.T. GUI-Based Floorplanning Tool

E N D

Presentation Transcript

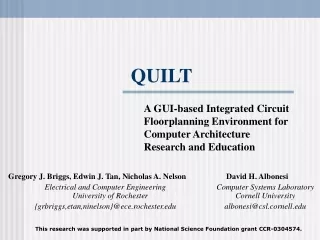

QUILT A GUI-based Integrated Circuit Floorplanning Environment forComputer Architecture Research and Education Gregory J. Briggs, Edwin J. Tan, Nicholas A. Nelson Electrical and Computer EngineeringUniversity of Rochester {grbriggs,etan,ninelson}@ece.rochester.edu • David H. Albonesi • Computer Systems LaboratoryCornell University • albonesi@csl.cornell.edu This research was supported in part by National Science Foundation grant CCR-0304574.

OutlineQ U I L T = Quick Utility for IC Layout and Temperature modeling • Introduction • Description of QUILT • A few technical details • QUILT in the classroom • Future work • Conclusions Greg Briggs, University of Rochester

Introduction • An important part of our field is in making design tradeoffs • Performance • Cost • Power • Etc. • How can students gain experience with these concepts? Greg Briggs, University of Rochester

Introduction • How to gain experience? • Fabricate some chips • Time and money • FPGA emulation • Limited capacity • Internal structure is not very accurate with respect to many of the tradeoffs we are facing today • Interconnect delay • Power • Temperature • Simulation • Fast and reasonably accurate Greg Briggs, University of Rochester

Introduction • Popular simulators(i.e. SimpleScalar [3] + Wattch [2] + HotSpot thermal modeler [12]) • Command line / text based input • Tedious • Prone to bugs DTB1 0.000391000000000 0.000275000000000 0.000060750000000 -0.000663000000000 IntAlu2 0.000246750000000 0.000437000000000 0.000205000000000 -0.001650000000000 ROB 0.000346500000000 0.000469000000000 0.000451750000000 -0.001223000000000 Dcache 0.000778750000000 0.000938000000000 -0.000327000000000 -0.000388000000000 Greg Briggs, University of Rochester

Introduction • QUILT • Graphical interface • Architectural-level floorplan • Connects to HotSpot for thermal simulation (thermal performance directly limits power dissipation) • Interconnect estimation • More readily permits use of detailed simulators in the classroom Greg Briggs, University of Rochester

QUILT Interface Greg Briggs, University of Rochester

Floorplan Generation • New FUs • By Dimension • Automatic • Edit Modes • Move • Resize with constant area • Resize (no constraint) Greg Briggs, University of Rochester

Mode Demo Greg Briggs, University of Rochester

Unit Info • Transistor count • SRAM size • Chip area Greg Briggs, University of Rochester

Edit Menu Greg Briggs, University of Rochester

Interconnect Estimator • Electrical interconnect • Manhattan routing • Optical interconnect predictions • Point-to-point • Computes delays relative to cycle time Greg Briggs, University of Rochester

Connects with HotSpot [12] • Uses a “power trace file” for FU power dissipation inputs • Simply runs the “sim-template” program included with HotSpot 2.0 [7] Greg Briggs, University of Rochester

HotSpot Demo Greg Briggs, University of Rochester

Graphics Production • Useful for presentations, papers Greg Briggs, University of Rochester

Graphics Production • The “zoom effect” Greg Briggs, University of Rochester

A Few Technical Details • QUILT was written using Sun Java™ and its standard libraries. • Java object model makes the code easier to extend, and avoids bugs • Therefore, multi-platform • Tested fully under Linux and Windows • Packaged as a single JAR file which includes source code, yet you can run it just by double-clicking Greg Briggs, University of Rochester

Teaching and Research • GUI is better than text interface • Less error prone • More intuitive • More efficient and time saving • Engineering students have been shown to be visually-oriented and hands-on learners [5] Greg Briggs, University of Rochester

An Exercise Using QUILT • Students modify floorplans to create new proposed designs Area and interconnect delay estimates • Simulate via HotSpot / SimpleScalar or other simulator • View thermal results and produce graphics Greg Briggs, University of Rochester

Many Possible Exercises • Tradeoffs between temperature, performance, interconnect delay • Any exercise involving HotSpot becomes more feasible because of QUILT’s ease of use Greg Briggs, University of Rochester

Extensible / Future Work • Java object model makes it easier to add new functionality • Technology nodes • More accurate or new interconnect models • Floorplan macros • Online help • Etc. • Open source: the community is invited to extend this tool • www.ece.rochester.edu/research/acal/quilt/ Greg Briggs, University of Rochester

Conclusions • QUILT eases the study of interconnect delay and temperature (which limits power dissipation), two issues of importance for computer architects • QUILT avoids the hassle, debugging, and errors involved in text-based simulator set-up • Visualizations made by QUILT enhance learning Greg Briggs, University of Rochester

Questions? • For more information and downloads, please visit:www.ece.rochester.edu/research/acal/quilt/ • Thank You Greg Briggs, University of Rochester