Synthesizing TLM-2.0 Communication Interfaces

270 likes | 562 Vues

Synthesizing TLM-2.0 Communication Interfaces. Nadereh Hatami Paolo Prinetto Politecnico di Torino Dip. di Automatica e Informatica Torino, Italy. Goals. Propose a method to facilitate the synthesis of TLM 2.0 interfaces focusing on Direct Memory Interface (DMI)

Synthesizing TLM-2.0 Communication Interfaces

E N D

Presentation Transcript

Synthesizing TLM-2.0 Communication Interfaces Nadereh Hatami Paolo Prinetto Politecnicodi Torino Dip. di AutomaticaeInformatica Torino, Italy

Goals • Propose a method to facilitate the synthesis of TLM 2.0 interfaces focusing on Direct Memory Interface (DMI) • Propose an algorithm to automate the synthesis process. 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

Outline • Introduction • An overview on TLM 2.0 • TLM-2.0 Interface Synthesis approach • Case study • Conclusion 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

Outline • Introduction • An overview on TLM 2.0 • TLM-2.0 Interface Synthesis approach • Case study • Conclusion 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

Basic Levels of Abstraction Languages: Communication: Algorithmic Models C/C++, Matlab Shared Variables Transaction-Level Models Method Calls to Channels SystemC, SpecC, Metropolis Register Transfer Level Models Wires and Registers Verilog, VHDL Gate Level Models Layout

System Architecture Model System Requirements Requirements Document System Architecture Model Development System Architecture Model 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

Traditional Design Flow System Architecture Model Hardware Development HW Refinement and Test Software Design can not be started until the RT model is obtained RTL Software Design and Development SW Refinement and Test

TLM Based Design Flow System Architecture Model Transaction Level Model Development TLM Software Design and Development Hardware Validation and Verification Environment Development HW Refinement RTL

Why using TLM? • Simulates much faster than RTL • Represents key architectural components of hardware platform • Integrate hardware and software models • Early platform for software development • Software execution on virtual model of hardware platform • Early system exploration and verification • Available before RTL 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

Outline • Introduction • An overview on TLM 2.0 • TLM-2.0 Interface Synthesis approach • Case study • Experimental results • Conclusion 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

TLM 2.0 Components 1. Core interfaces and sockets * M. Montoreano. Transaction Level Modeling using OSCI TLM 2.0. Technical report, Open SystemC Initiative, 31 May 2007. Initiator Target 2. Generic payload 3. Base protocol Command Address Data Byte enables Response status BEGIN_REQ END_REQ BEGIN_RESP Extensions END_RESP 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

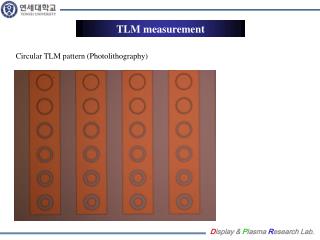

Direct Memory Interface Direct Memory Interface: • Gives an initiator a direct pointer to memory in a target • By-passes the sockets and transport calls • Read or write access by default • Extensions may permit other kinds of access • Target responsible for invalidating pointer 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

Outline • Introduction • An overview on TLM 2.0 • TLM-2.0 Interface Synthesis approach • Case study • Conclusion 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

TLM 2.0 Synthesis Untimed Loosely-Timed Approximately-Timed RTL 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

TLM 2.0 Synthesis Untimed Loosely-Timed Approximately-Timed Intermediate Layer RTL 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

TLM 2.0 Direct Memory Interface Synthesis DMI Access DMI Request Initiator Inter connect DMI Request Target DMI Pointer DMI Pointer

TLM 2.0 Direct Memory Interface Synthesis DMI Access DMI Request Initiator Inter connect DMI Request Target DMI Pointer DMI Pointer Arbiter Sc_export DMA Channel Target Inter connect Initiator 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

TLM 2.0 DMI Synthesis Algorithm • With respect to socket synthesis algorithm, synthesize the socket to a port and an export • Put the DMA custom channel between the initiator and the interconnect connected to it. • If the original socket is target, change the port’s interface to tlm_nonblocking_get_if 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

TLM 2.0 DMI Synthesis Algorithm(cont’d) • Change the port and export interfaces with respect to their type: tlm_put_if for initiator sockets and tlm_get_if for target sockets • Put an arbiter between the target and the interconnect connected to it. The other port of arbiter will be connected to DMA channel. 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

Outline • Introduction • An overview on TLM 2.0 • TLM-2.0 Interface Synthesis approach • Case study • Conclusion 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

Simulation Time Comparison 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

Outline • Introduction • An overview on TLM 2.0 • TLM-2.0 Interface Synthesis approach • Case study • Conclusion 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

Conclusion • Defining an intermediate layer containing necessary details for synthesis. • TLM-1.0 components were chosen to describe the intermediate layer. • Algorithms are proposed to map the interfaces in TLM-2.0 standard to TLM-1.0 channels • Experiments verify the correctness of the proposed algorithms 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

Conclusion (cont’d) • The proposed method: • simplifies the transition from transaction level to lower level • speeds up the whole process. 7th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM

Cпаcибo!!! Малые Автюхи, Калинковичский район, Республики Беларусь