Understanding Clock Speed in Synchronous Sequential Circuits

In this lecture, Prof. Taeweon Suh from Korea University delves into the fundamentals of clock speed and its significance in synchronous sequential circuits. We explore the operating clock frequencies of various processors, uncovering the reasons behind the different clock speeds of CPUs. The discussion includes key concepts such as setup time, hold time, and propagation delay, critical for understanding how circuits operate at specific frequencies. Additionally, we examine timing analysis and constraints necessary for achieving optimal performance in digital systems.

Understanding Clock Speed in Synchronous Sequential Circuits

E N D

Presentation Transcript

2010 R&E Computer System Education & Research Lecture 5. Sequential Logic 3 Prof. Taeweon Suh Computer Science Education Korea University

What Determines Clock Speed? • What is the operating clock frequency of your computer? • Why does the atom processor on your netbook run at 1.4GHz? • Why does the Core 2 Duo on your notebook run at 2.0GHz? • Why can’t run at 100GHz or 1000GHz? • We are going to answer to this question today

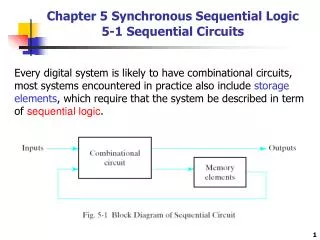

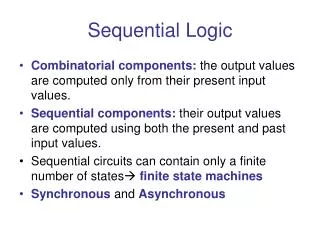

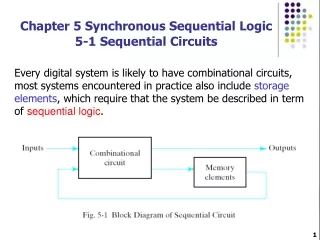

Synchronous Sequential Circuit • As studied, virtually all the synchronous sequential circuits (including CPU) are composed of • Flip-flops cascaded • Combinational logic between flip-flops • Pipeline is also implemented in this way • We are going to talk deep about this in computer architecture class next semester Q3 D2 Q2 D3 D1 CL1 CL2 R1 R3 R2

Short Answer • Suppose that the circuit does addition (+1) to the input (D1) • CL1 does “+1” • So, we want to get “D1+1” after 1 clock cycle D2 Q2 D1 CL1 R1 R2 If delay is shorter than 1ns, the circuit can run at 1GHz If delay is longer than 1ns, the circuit can’t run at 1GHz CL1 delay CL1 delay

A Little Long Answer • Let’s talk a little deep about what contributes to the delay • Consequently what determines the clock frequency of synchronous sequential circuit

Timing • Flip-flop samples D at the (rising) edge of the clock • Input data in D must be stable when it is sampled • Similar to a photograph, input data must be stable around the clock edge • If input data is changing when it is sampled, metastability can occur

Input Timing Constraints • Setup time • tsetup = time before the clock edge that data must be stable • Hold time • thold= time after the clock edge that data must be stable • Aperture time • ta = time around clock edge that data must be stable (tsetup + thold)

Output Timing of Flip-Flop • Propagation delay • tpcq= time after clock edge that the output Q is guaranteed to be stable (i.e., to stop changing) • Contamination delay • tccq= time after clock edge that Q might be unstable (i.e., start changing) • Output timing is determined depending on how you implement flip-flop

Dynamic Discipline • The input to a synchronous sequential circuit must be stable during the aperture (setup and hold) time around the clock edge. • Specifically, the input must be stable • at least tsetup before the clock edge • at least until thold after the clock edge

Dynamic Discipline • The delay between registers has a minimum and maximum delay, dependent on the delays of the circuit elements

Setup Time Constraint • The setup time constraint depends on the maximum delay from register R1 through the combinational logic • The input to register R2 must be stable at least tsetup before the clock edge Tc ≥ tpcq + tpd + tsetup tpd ≤ Tc – (tpcq + tsetup)

Hold Time Constraint • The hold time constraint depends on the minimum delay from register R1 through the combinational logic • The input to register R2 must be stable for at least thold after the clock edge tccq + tcd > thold tcd > thold - tccq

Timing Analysis Example Timing Characteristics tccq = 30 ps tpcq = 50 ps tsetup = 60 ps thold = 70 ps tpd = 35 ps tcd = 25 ps

Timing Analysis Example Timing Characteristics tccq = 30 ps tpcq = 50 ps tsetup = 60 ps thold = 70 ps tpd = 35 ps tcd = 25 ps Tc ≥ tpcq + tpd + tsetup tccq + tcd > thold Setup time constraint: tpd = 3 x 35 ps = 105 ps Tc ≥ (50 + 105 + 60) ps = 215 ps fc = 1/Tc = 4.65 GHz Hold time constraint: tccq + tcd > thold ? (30 + 25) ps > 70 ps ? No!

Fixing Hold Time Violation Add buffers to the short paths: Timing Characteristics tccq = 30 ps tpcq = 50 ps tsetup = 60 ps thold = 70 ps tpd = 35 ps tcd = 25 ps Tc ≥ tpcq + tpd + tsetup tccq + tcd > thold Setup time constraint: tpd = 3 x 35 ps = 105 ps Tc ≥ (50 + 105 + 60) ps = 215 ps fc = 1/Tc = 4.65 GHz Hold time constraint: tccq + tcd > thold ? (30 + 50) ps > 70 ps ? Yes!