Pipeline with Data Forwarding

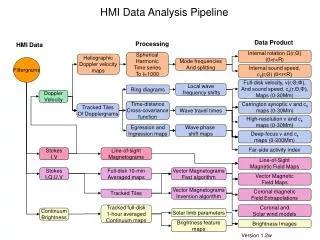

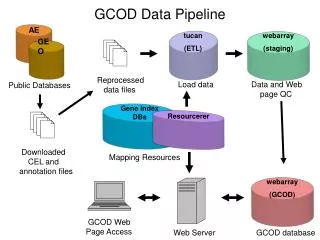

This document discusses the challenges of data hazards in pipelined architectures and proposes solutions using data forwarding techniques. It presents a detailed example of a loop involving various operations like addition, load, and store instructions. The original version exhibits unavoidable data hazards causing pipeline stalls. The paper analyzes the impact of these stalls on performance and explores the possibility of reordering instructions to minimize or eliminate delays. The final section illustrates a revised instruction flow that effectively reduces data hazards.

Pipeline with Data Forwarding

E N D

Presentation Transcript

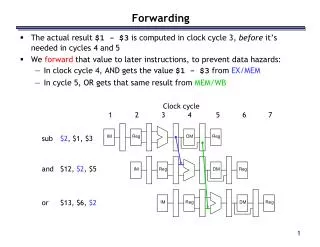

Solving Data hazards Pipeline with Data Forwarding

C O N T R O L M U X A D D A D D 4 Sh L 2 Registers PC Instruction Memory A L U M U X Data Memory Sign Ext M U X ALU CTL M U X IF ID/RF EXE MEM WB

Data Hazards • Loop: addi $t0, $t0, 4 • beq $t0, $s1, endLoop • add $t1, $t0, $s0 • add $t2, $t0, $s4 • lw $t3, 0($t1) • lw $t4, 0($t2) • add $t3, $t4, $t3 • sw $t3, 0($t1) • j Loop • endLoop:

C O N T R O L M U X A D D A D D 4 Sh L 2 Registers PC Instruction Memory A L U M U X Data Memory Sign Ext M U X ALU CTL M U X IF ID/RF EXE MEM WB

C O N T R O L M U X A D D A D D 4 Sh L 2 Registers PC Instruction Memory A L U M U X Data Memory Sign Ext M U X ALU CTL M U X IF ID/RF EXE MEM WB

M U X M U X HAZARD M U X CTRL 0 A D D 4 = Reg Instruct Memory PC A L U M U X Data Memory Sign Ext M U X FRWD ALU CTL M U X IF ID/RF EXE MEM WB

C O N T R O L M U X A D D A D D 4 Sh L 2 Registers PC Instruction Memory A L U M U X Data Memory Sign Ext M U X ALU CTL M U X IF ID/RF EXE MEM WB

M U X M U X HAZARD M U X CTRL 0 A D D 4 = Reg Instruct Memory PC A L U M U X Data Memory Sign Ext M U X FRWD Branch forwarding ALU CTL M U X IF ID/RF EXE MEM WB

Unavoidable data hazards • lw data to immediately following instruction • one cycle stall • ALU to immediately following branch • one cycle stall • lw to immediately following branch • two cycle stall • Stalls need circuits to freeze PC and to place 0’s in control line registers

Unavoidable Data Hazards • Loop: addi $t0, $t0, 4 • beq $t0, $s1, endLoop • add $t1, $t0, $s0 • add $t2, $t0, $s4 • lw $t3, 0($t1) • lw $t4, 0($t2) • add $t3, $t4, $t3 • sw $t3, 0($t1) • j Loop • endLoop: Can we reorder code to fix??

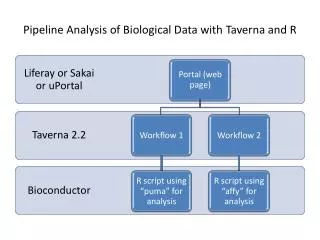

Reordered • addi $t0, $t0, 4 • Loop: add $t1, $t0, $s0 • beq $t0, $s1, endLoop • add $t2, $t0, $s4 • lw $t3, 0($t1) • lw $t4, 0($t2) • addi $t0, $t0, 4 • add $t3, $t4, $t3 • sw $t3, 0($t1) • j Loop • endLoop: No longer a problem

M U X M U X HAZARD M U X CTRL 0 A D D 4 = Reg Instruct Memory PC A L U M U X Data Memory Sign Ext M U X FRWD Branch forwarding ALU CTL M U X IF ID/RF EXE MEM WB