Understanding Interrupts and Resets in Microcontroller Systems

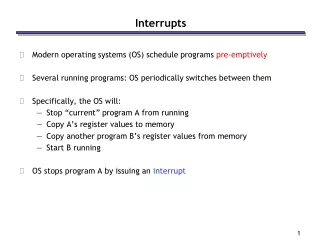

This guide covers the fundamental concepts of interrupts and resets, particularly within the context of the HC11 microcontroller. In-class activities will demonstrate polling versus interrupt-driven I/O. Key topics include the mechanisms of interrupts, their importance in multitasking, the difference between interrupts and subroutines, and the management of interrupt priority. It includes hands-on examples with button presses to illustrate software switch debouncing and the efficient handling of CPU resources to maximize performance.

Understanding Interrupts and Resets in Microcontroller Systems

E N D

Presentation Transcript

Interrupts, Resets • Today: • First Hour: Interrupts • Section 5.2 of Huang’s Textbook • In-class Activity #1 • Second Hour: More Interrupts • Section 5.2 of Huang’s Textbook • In-class Activity #2

Computer (HC11 chip) 4-bit Data Source Display Push Button Example Task Read the output of the 4-bit data source every time the push button is pressed, and display the result.

START BUTTON PRESSED? NO Computer (HC11 chip) 4-bit Data Source YES 1 ms delay Display BUTTON PRESSED? NO Push Button YES READ 4-BIT INPUT UPDATE DISPLAY One Method... Why do we have this? Software switch debouncing This style of computer input/output is called Polled I/O because we’re constantly polling the pushbutton

Eats up a lot of CPU cycles doing nothing! We’re repeatedly checking the button Each time the button is pressed, we delay by 1 ms by going around in a loop, wasting time This is also called “busy wait” We could do better if only we could somehow grab the CPU’s attention momentarily whenever the button is pressed! We could do even better if the 1 ms delay could be achieved without a delay loop! Is Polling Bad?

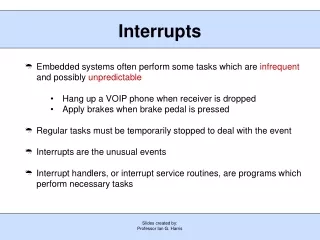

Introducing Interrupts A mechanism to interrupt the CPU, i.e., steal it for a little while to service the interrupting device (a button in our example)

Why are Interrupts Important? They allow multiple processes to run on a computer They allow the CPU to be shared, greatly extending its ability For example, the CPU can be doing something else when “waiting” for the button to be pressed

useful or otherwise.... START INITIALIZE Key Pressed Computer (HC11 chip) 4-bit Data Source DO SOMETHING USEFUL Display Push Button Interrupt Method Suppose that the computer is doing something... DO SOMETHING USEFUL

The CPU is temporarily interrupted. An Interrupt Service Routine is entered START INTERRUPT SERVICEROUTINE Key Pressed START INITIALIZE READ THE 4-BIT INPUT UPDATE THE DISPLAY DO SOMETHING USEFUL RETURNFROM INTERRUPT Interrupt Method START INTERRUPT SERVICEROUTINE READ THE 4-BIT INPUT UPDATE THE DISPLAY DO SOMETHING USEFUL RETURNFROM INTERRUPT The CPU now resumes where it left off!

Interrupts are Transparent The program that was interrupted does not have a clue that it was interrupted!! Interrupt Service Routines need to leave registers untouched Interrupt Service Routines need to be extremely short and quick WHY??

Interrupts vs. Subroutines Interrupt Service routines may look a bit like subroutines, but they are very different. Subroutines are not transparent.The calling routine is aware of the subroutine call. Interrupt Service Routines are initiated by hardware, with some exceptions (e.g., SWI). The CPU hardware automatically saves and restores all registers. With subroutines, the programmer has to write code for saving and restoring. In general, not all registers are saved.

Interrupt Sources Interrupts can come from several sources Hardware Sources External Pushbuttons Timers Serial Communication Systems ... Software Sources SWI instruction

Interrupt Priority Different Sources can have different priorities For example, sources requiring a more timely response get higher priority. At 9600 bits/sec, the RS-232 port on your PC produces an interrupt about once every 2000 CPU cycles. The 68HC11 timer produces an interrupt once every 216 CPU cycles. The timer has higher priority in this case.

Interrupts: Recap • What is an interrupt? • A special event that requires the CPU to stop normal program execution and perform some service related to the event. • E.g.: I/O completion, timer time-out, illegal opcodes, arithmetic overflow, divide-by-0 etc. • Functions of Interrupts: • - Coordinating I/O activities and preventing CPU from being tied up • - Providing a graceful way to exit from errors • - Reminding the CPU to perform routine tasks

Managing Interrupts • Interrupt Maskability: • - Interrupts that can be ignored by the CPU are called maskable interrupts. • A maskable interrupt must be enabled before it can interrupt the CPU. • An interrupt is enabled by setting an enable flag. • Interrupts that can’t be ignored by the CPU are called non-maskable interrupts. • Interrupt priority: • - The order in which the CPU will service interrupts when all of them occur at the same time. Why do we need to use masking and priority to manage interrupts ?

68HC11 Interrupts The 68HC11 supports 16 hardware interrupts and two software interrupts. Hardware Interrupts Software interrupts: SWI instruction, and illegal opcode interrupt. Both are nonmaskable.

When an interrupt request is detected by the CPU, it needs a way to find out the source of the interrupt. One approach: Polling Better approach: Vectored interrupts Interrupt Vector: The starting address of the interrupt service routine (ISR), stored in a standard location. Who is it??

Vector address Interrupt source Priority FFC0, C1 reserved . . . . . . FFD4, D5 reserved lowest FFD6, D7 SCI serial system FFD8, D9 SPI serial transfer complete FFDA, DB pulse accumulator input edge FFDC, DD pulse accumulator overflow FFDE, DF timer overflow FFE0, E1 timer output compare 5 FFE2, E3 timer output compare 4 FFE4, E5 timer output compare 3 FFE6, E7 timer output compare 2 FFE8, E9 timer output compare 1 FFEA, EB timer input capture 3 FFEC, ED timer input capture 2 FFEE, EF timer input capture 1 FFF0, F1 real timer interrupt FFF2, F3 IRQ pin interrupt FFF4, F5 XIRQ pin interrupt FFF6, F7 SWI FFF8, F9 illegal opcode trap FFFA, FB COP failure FFFC, FD COP clock monitor fail highest FFFE, FF RESET Eg: 6811 Int. Vector Address & Priority Whenever timer overflows, the CPU executes the ISR starting at address stored here.

Jump to ISR Implementing Interrupts • Interrupt Service Routine (ISR): • Piece of code which handles the interrupt • Interrupt Vector: • Starting address of the interrupt service routine • Interrupt Vector Table: • A table where all interrupt vectors are stored. • Similar to I/O Jump Table ISR Code Interrupt Vector Address ISR Address

1. Saving the program counter value in the stack 2. Saving the CPU status (including the CCR register and some other registers) in the stack 3. Identifying the cause of interrupt 4. Resolving the starting address of the corresponding interrupt service routine through the Interrupt Vector Table 5. Executing the interrupt service routine (ISR) 6. Restoring the CPU status and the program counter from the stack 7. Restarting the interrupted program Interrupt Service Cycle

Do Activity #2 Now • Due: End of Class Today. • RETAIN THE LAST PAGE(S) (#3 onwards)!! • For Next Class: • Bring Huang Textbook, & HC11 PRG • Required Reading: • Sec 4.1-4.7 of Huang • This reading is necessary for getting points in the Studio Activity!