Implementing Timer Interrupts with ACLK and CCR for MSP430 in Upmode Configuration

This technical guide outlines the setup and operation of timer interrupts for the MSP430 microcontroller using ACLK (32.768kHz) in upmode. It covers various scenarios, including case A, B, and C, with detailed commands for clearing timers and enabling CCR1, CCR2, and overflow interrupts. Each case features specific patterns and timing operations, ensuring precise control of timer functions. The configuration settings are crucial for optimizing operation and achieving reliable timing sequence execution.

Implementing Timer Interrupts with ACLK and CCR for MSP430 in Upmode Configuration

E N D

Presentation Transcript

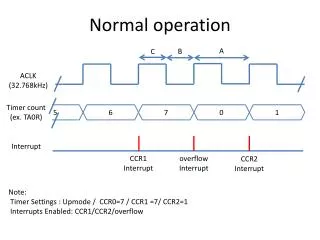

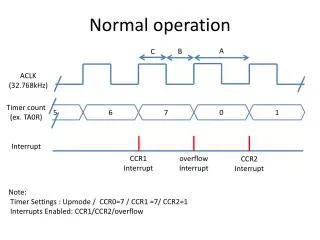

Normal operation A B C ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 0 1 Interrupt CCR1 Interrupt overflow Interrupt CCR2 Interrupt Note: Timer Settings : Upmode / CCR0=7 / CCR1 =7/ CCR2=1 Interrupts Enabled: CCR1/CCR2/overflow

Case A: Pattern1Timer is cleared in A duration command : TA0CTL |= (MC_1 | TACLR); Timer Clear ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 0 1 0 Interrupt CCR1 Interrupt overflow Interrupt CCR2 Interrupt

Case A: Pattern 2Timer is cleared in A duration command : TA0CTL |= (MC_1 | TACLR); Timer Clear ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 0 0 Interrupt CCR2 Interrupt CCR1 Interrupt overflow Interrupt

Case B: Pattern 1Timer is cleared in B duration command : TA0CTL |= (MC_1 | TACLR); Timer Clear ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 0 2 1 Interrupt CCR1 Interrupt CCR2 Interrupt

Case B: Pattern2Timer is cleared in B duration command : TA0CTL |= (MC_1 | TACLR); Timer Clear ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 0 0 1 Interrupt CCR2 Interrupt CCR1 Interrupt

Case B: Pattern3Timer is cleared in B duration command : TA0CTL |= (MC_1 | TACLR); Timer Clear ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 0 1 Interrupt CCR2 Interrupt CCR1 Interrupt

Case B: Pattern4Timer is cleared in B duration command : TA0CTL |= (MC_1 | TACLR); Timer Clear ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 1 2 Interrupt CCR2 Interrupt CCR1 Interrupt

Case C: Pattern 1Timer is cleared in C duration command : TA0CTL |= (MC_1 | TACLR); Timer Clear ACLK (32.768kHz) Timer count (ex. TA0R) 0 5 6 7 1 2 Interrupt CCR1 Interrupt CCR2 Interrupt

Case C: Pattern 2Timer is cleared in C duration command : TA0CTL |= (MC_1 | TACLR); Timer Clear ACLK (32.768kHz) Timer count (ex. TA0R) 0 5 6 7 0 1 Interrupt CCR2 Interrupt CCR1 Interrupt

Case C: Pattern3Timer is cleared in C duration command : TA0CTL |= (MC_1 | TACLR); Timer Clear ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 0 2 1 Interrupt CCR2 Interrupt CCR1 Interrupt

Case C: Pattern4Timer is cleared in C duration command : TA0CTL |= (MC_1 | TACLR); Timer Clear ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 0 1 0 Interrupt CCR2 Interrupt CCR1 Interrupt

Case C: Pattern5Timer is cleared in C duration command : TA0CTL |= (MC_1 | TACLR); Timer Clear ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 1 2 Interrupt CCR2 Interrupt CCR1 Interrupt

Case C: Pattern6Timer is cleared in C duration command : TA0CTL |= (MC_1 | TACLR); Timer Clear ACLK (32.768kHz) Timer count (ex. TA0R) 5 6 7 0 1 Interrupt CCR2 Interrupt CCR1 Interrupt