Functional Verification of Hardware Designs

160 likes | 544 Vues

Functional Verification of Hardware Designs. EE764 – Functional Verification of Hardware Designs Course Objectives Learn to use verification tools and experiment on actual circuits designed in industry Learn to plan & carry out effective functional verification of a design

Functional Verification of Hardware Designs

E N D

Presentation Transcript

Functional Verification of Hardware Designs • EE764 – Functional Verification of Hardware Designs • Course Objectives • Learn to use verification tools and experiment on actual circuits designed in industry • Learn to plan & carry out effective functional verification of a design • Learn to work in teams to debug designs • May even both code and debug ©2008 Joanne DeGroat, ECE, OSU

Functional Verification of Hardware Designs (cont) • By the end of the course the student will have • Verified several examples provided by the instructor (some may come from industry) • Have an understanding of why verification is important • Have an understanding of the level of complexity present in the verification of modern microcircuits ©2008 Joanne DeGroat, ECE, OSU

Syllabus/Grading/Project • Syllabus • Projects • Project 1 – Floating Point Adder • Project 2 – Floating Point Multiplier • Students will work on projects 1, 2 in a group of two. Each is due 2 weeks from when assigned • Project 3 – Floating Point Execution Sub Unit controller • Project 4 – Floating Point Execution Sub Unit. • Students will work on projects 3 and 4 in a group of three. Each will be due three weeks from when assigned. ©2008 Joanne DeGroat, ECE, OSU

History 101 • VHDL 1st standardized in 1987 by IEEE • VHDL about to be standardized again and will include many new aspects, several aimed specifically aimed toward verification (PSL) • Verilog 1st standardized in 1995 by IEEE • Hardware Description Languages were the beginning of several new advances in chip and system design • Simulation of chips and systems • Synthesis of digital hardware • Verification ©2008 Joanne DeGroat, ECE, OSU

History continued • 1990 focus – Does chip work at all? • 2000 focus – Does chip work in the system environment as specified? • Today – more efficient verification than in 2000. ©2008 Joanne DeGroat, ECE, OSU

Level of complexity problem From www.chipexpress.com Note that this was a 2003 chart!!! ©2008 Joanne DeGroat, ECE, OSU

Today’s design issue • Gate counts and system complexity growing exponentially • Bulk of time in design of an new IC is spent on verification • In most companies there is at least a 1-to-1 ratio of design engineers to verification engineers. • Real problem is not how to create the 12 million gate IC but how to verify it. ©2008 Joanne DeGroat, ECE, OSU

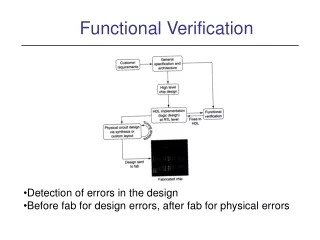

What is verification? • Verification is not a testbench or a series of testbenches. • Verification is a process used to demonstrate the functional correctness of a design. It is the act of ensuring that the logic design conforms to the specifications. • Verification does not insure that the specification is correct. (Next real advance in design will likely be specification languages! – Note new topics in text – Open Vera and e!) ©2008 Joanne DeGroat, ECE, OSU

Testbenches • VHDL (and Verilog) testbenches refer to the code used to create an input sequence to the design under test (DUT) and optionally observe the response. • In EE762 the testbenches do both and the error signal indicates that the results do not equal what is expected. ©2008 Joanne DeGroat, ECE, OSU

Verification testbenches • In verification the testbench provides the inputs and monitors the outputs. • The challenge of verification is to determine what input patterns to supply and what is the expected output of a properly working design Testbench Design under verification ©2008 Joanne DeGroat, ECE, OSU

EE762 testbenches • The testbenches used in EE762 check the essentials of basic correct operation and are less than a typical verification testbench. The goal of the EE762 testbenches is to catch typical mistakes, check the operation in central and corner cases, and provide feedback to the student (the error signal). • They are somewhat less than a testbench to be used for production of an IC. ©2008 Joanne DeGroat, ECE, OSU

Verification Cycle DESIGN Develop Environment Create Testplan Debug Design Escape Analysis Regression Hardware Debug RIT ©2008 Joanne DeGroat, ECE, OSU

Verification Testplan • Schedule • Required tools • Input and completion criteria • Specific tests • What is expected to be found with each test • What’s not covered by the tests ©2008 Joanne DeGroat, ECE, OSU

Other parts of cycle • RIT – stands for Release Interface Tape • RIT is sending the design to the chip fab. • Chip is fabricated and then IC is tested. • Escape Analysis – Fully understand any bugs in fabricated part. • A critical part of the IC verification process • Reproduce in simulation if possible • Lack of ability to reproduce means fix cannot be verified • Could misunderstand the bug ©2008 Joanne DeGroat, ECE, OSU

Todays Work • Form into your group of two. • Read Chapter 1 of text • Assignment will be covered Wednesday. • Verification of a Floating Point Adder. • Behavioral and synthesis model provided. ©2008 Joanne DeGroat, ECE, OSU

Alternative project flow • Projects • Project 1 – Floating Point Adder • Project 2 – Redefinition of Datapath unit or other unit • Given the specification student will both write the design from a specification while part of the group designs up the verification suite and performs the verificaton. • Very much like the “real” world • Upside – a very real world situation of design and verification • Downside – possibly more total work and lower complexity units to verify (but only slightly) • Project 3 – Expanded datapath ©2008 Joanne DeGroat, ECE, OSU