Ground and Power Planes

260 likes | 502 Vues

Ground and Power Planes. Chris Allen (callen@eecs.ku.edu) Course website URL people.eecs.ku.edu/~callen/713/EECS713.htm. Ground planes. Ground planes were assumed in previous discussions discussion on vias layer stack up (MCMs) microstrip and stripline transmission line

Ground and Power Planes

E N D

Presentation Transcript

Ground and Power Planes Chris Allen (callen@eecs.ku.edu) Course website URL people.eecs.ku.edu/~callen/713/EECS713.htm

Ground planes • Ground planes were assumed in previous discussions • discussion on vias • layer stack up (MCMs) • microstrip and stripline transmission line • Ground planes serve several functions • return path for signal current • stable voltage reference • Focus here will be primarily on return path and crosstalk

Ground planes • Ground planes as current return path • DC current flows along path of least resistance • Consider the circuit for I0 = 1 A I1 = I0 1000/1001 = 0.999 A I2 = 1 mA • for AC (f > 0) current follows the path of least impedance • Z = R + jX XL = L , XC = -1/C • As discussed previously, inductance compels the return path current to flow beneath • the signal trace (proximity effect)

Ground planes • For microstrip transmission lines • at frequencies where L >> R • the distribution of return current follows small H, the current is more concentrated large H, the current is less concentrated • For striplines • the current follows a similardistribution based on howthe current is split between the two return paths

Ground planes • Return-path current and crosstalk • Adjacent transmission lines can experience crosstalk as the current (and resulting magnetic field) induces a signal in the passive (inactive) trace • The induced crosstalk falls off with the square of the increasing distance • Where • K = f (Tr, trace length) < 1K can be determined experimentally • Unless K is known, we will assume K = 1 to be conservative

Ground planes • Return-path current and crosstalk

Ground planes • Return-path current and crosstalk • Interruptions in the ground plane that prevent electrical continuity disrupt current flow effectively lengthening the return path This increase in circuit loop area increases the path inductance by L D is the slot length (the perpendicular extent of the current diversion away from the signal trace) in inches W is the trace width, in inches

Ground planes • Effects of ground-plane interruptions • Increases signal rise time Similar to L-R circuit • assumes resistance on either side of inductance is Zo • Increases crosstalk due to current coupling to nearby traces • Clearly breaks in the ground plane cause problems • So why would designer break ground plane continuity?Perhaps to route signals that won’t ‘fit’ on other routing layers • Note: the phenomenon of breaks in the ground plane increasing path inductance is used in non-destructive tests to locate metal fatigue wherein micro-cracks disrupt surface current flow resulting in magnetic fields uncharacteristic of solid conductors

Ground planes • Effects of ground-plane interruptions • Example – slotted ground plane 10G GaAs technology, Tr = 150 ps Zo = 50 Trace width, 10 mils (0.010”) Tr due to slot, total Tr, D = 0.25”

Ground planes • Examples of discontinuous ground plane • Ground plane grid scheme Saves board area at expense of mutual inductance Power dist on top layer / GND on bottom Fine for low-speed CMOS and TTL High-freq return-path current uses bypass capacitorsto stay near signal currenton way back to drive gate

Ground planes • Examples of discontinuous ground plane • Ground fingers layout Returning signal currents must go all the way around the board edge resulting in massive amounts of self-inductance and mutual inductance Power and ground wiring on single layer Found in prototyping circuit boards Works well with low-speed logic

Ground planes • Grounded guard traces • Guard traces between signal traces may reduce crosstalk Coupling between adjacent microstrip line can be halved, if sufficient space is available, by inserting between them a third trace (grounded at both ends), called a guard trace,. Coupling can be halved again if this guard trace is connected to the ground plane at frequent intervals. • However the best way to manage crosstalk is provide adequate separation and provide continuous ground plane

Ground planes • Near-end and far-end crosstalk • The coupled signal on the passive trace has different characteristics when viewed from the near end vs. the far end continuous coupling or discrete coupling regions

Ground planes • Near-end and far-end crosstalk • First the inductive crosstalk Consider a positive-going step Transient induces current in ckt C-D Forward-going negative ‘blips’ prop at same velocity as driving signal so theyadd constructively (similar to how shock waves add to form sonic boom) Reverse-going positive ‘blips’ have distributed start times and travel times blips blend into one long, low blob

Ground planes • Near-end and far-end crosstalk • Now the capacitive crosstalk Again a positive-going step Transient couples current in ckt C-D Forward-going positive ‘blips’ prop at same velocity as driving signal add constructively Again, reverse-going positive ‘blips’ have distributed start times and travel times blips blend into one long, low blob Note the positive polarity of the capacitively-coupled blips

Ground planes • Near-end and far-end crosstalk • Normally the inductive and capacitive crosstalk voltages are of comparable magnitude The forward crosstalk components should therefore cancel at the far end The reverse crosstalk components reinforce at the near end • Stripline circuits are typically well balanced between inductive and capacitive coupling while microstrip lines generally have slightly less capacitive coupling than inductive • Reverse-coupled signals can become an issue if the near-end impedance mismatch is significant Example shows reverse-coupled signal reflected from a low-impedance (Rs < Zo –1)driver

Ground planes • Near-end and far-end crosstalk • Example – coupled 50- microstrip lines w = 15 mils, h = 10 mils, D = 45 mils, ℓ = 1.5” • for GaAs technology, V = 1.5 V, Tr = 150 ps crosstalk V = 71 mV For delay = 180 ps/in, Tp = 270 ps Vc = Area/2Tp = 10.6x10-12/540 ps = 19.6 mV Capacitive crosstalkeffectively cancels blip at Ddoubles crosstalk at C 39 mVif source impedance, Rs = 8 s = -0.72, at 3Tp (810 ps), -28 mV (1.9% of V)

Power planes • Power planes • Good idea to dedicate a power plane for each supply voltage that is used widely example: ECL designs VEE = -4.7 V and VTT = -2 V • Substantial currents pass through these planes (several amps) 1 oz. or 2 oz. copper should be used Desired properties: low resistance, low inductance • To connect components to power, simply sink a via to the appropriate power plane • One power plane per voltage is generally adequate

Board stack-up of layers • Designing a stack-up of layers • N: number of conducting layers • A double-sided board has N = 2 • A multilayer board has N>2 layers

Board stack-up of layers • Multilayer circuit board • Normally vias penetrate entire stack • Blind or buried vias may also be used Blind vias begin on one surface but do not penetrate the board thickness Buried vias begin and end on internal layers

Board stack-up of layers • Multilayer circuit board • Routing issues Components are mounted on outer layers (exceptions are buried components) Surface-mounted components don’t require vias for each device pin Permits higher density component placement and signal routing Through-hole components require vias for component leads these vias obstruct routing paths on internal and backside layers Thermal vias beneath components also obstruct routing paths on internal and backside layers When routing signals on the 2 outer layers, components obstruct routing, often requiring internal routing layers

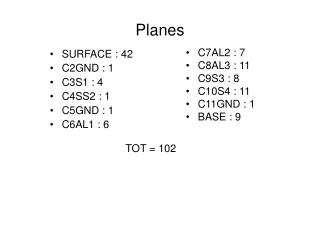

Board stack-up of layers • Example multilayer circuit board stack-ups

Board stack-up of layers • Example multilayer circuit board stack-ups

Board stack-up of layers • Example multilayer circuit board stack-ups • To minimize warping, it is desirable for the stack-up to be symmetrical (this example is symmetric) • Thinner copper layers enable more precise stripline trace widths • Thicker power planes provide lower resistance

Signal routing layers • Routing layers • Signal routing on layers are usually divided into x (east-west) andy (north-south) trace directions • Maximizes utilization of limited routing space • Lower speed signals can share adjacent layers (since crosstalk is not an issue) • For high-speed signal routing, layout rules must be specified Trace width, W Minimum trace separation, S,(assumes r, and b or h are known) Metal thickness, t, from copper weight (1/2 oz. or 1 oz.) Ground and power planes may use 1 oz. or 2 oz. copper for lower resistance

Signal routing layers • Routing layers • How many routing layers are needed? • Observed relationship: Rent’s rule for a board width, X board height, Y average trace pitch, pavg number of signals (connections), N number of routing layers, M • X, Y, and N known from system constraints • W, D determined from Zo and crosstalk analysis minimum pavg is known • Leaves M (number of routing layers) as the unknown • Example, W = 15 mils, S = 45 mils pavg = 0.06N = 150, X = 3”, Y = 3” M = 1.1 = 2 Rent’s rule says at least 2 routing layers needed pitch = D = S + W