Processor External Interrupt Verification Tool (PEVT)

Processor External Interrupt Verification Tool (PEVT). Fu-Ching Yang, Wen-Kai Huang and Ing-Jer Huang Dept. of Computer Science and Engineering National Sun Yat-Sen University, Kaohsiung Taiwan. Dabort. FIQ. IRQ. Pabort. Pabort. Pabort. FIQ. IRQ. Fetch. Execute2. Decode. Execute1.

Processor External Interrupt Verification Tool (PEVT)

E N D

Presentation Transcript

Processor External Interrupt Verification Tool (PEVT) Fu-Ching Yang, Wen-Kai Huang and Ing-Jer Huang Dept. of Computer Science and Engineering National Sun Yat-Sen University, Kaohsiung Taiwan

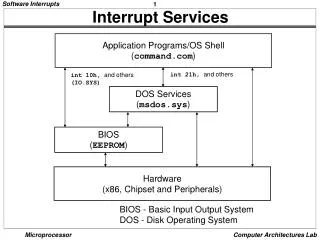

Dabort FIQ IRQ Pabort Pabort Pabort FIQ IRQ Fetch Execute2 Decode Execute1 Execute3 FIQ Fetch Decode Hold Hold Execute IRQ Abort Decode Fetch Execute Motivation • Microprocessor verification • Instruction-based verification • Branch prediction, Data hazard, etc… • External interrupt verification • Why the external interrupt verification requires automation • External interrupt is an unexpected event • Tightly related to instruction • Trigger timing must be precise • Pipelined behavior must keep precise ? RTN. addr. INT. vector SRV. Processor Add instruction MPEG JPEG Sub instruction

Comparison with manual approach • Processor External Interrupt Verification Tool (PEVT) • Automatically insert external interrupt signals • Automatically insert instructions • Automatically verify the microprocessor • RTL level • Cycle accurate • Time-efficiency • High functional coverage

IRQ IRQ IRQ 3-cycle instruction Load Fetch Decode Execution3 Execution Execution2 3 cycles Proposed Verification Framework • Required micro-architecture information • Microprocessorpipeline stages • Instruction cycles • External interrupt information • Instruction’s relationship with external interrupt INT. Vector Execution1

Proposed Verification Framework • Exception Description Language (EXPDL) • Microprocessor model • Assertion rule database • Processor-independentverification rules • Extendable • Individual interrupt • Concurrent interrupt • Nested interrupt • PEVT generates verification cases • Combine EXPDL andassertion rule database • For automatic RTL verification • Generate trigger • Comprise HW and SW • Generate monitor hardware Automatic External Interrupt HW/SW Generation

Automatic External Interrupt HW/SW Generation Automatic External Interrupt HW/SW Generation Exception Description Languages (EXPDL) • Architecture Description Language • LISP-like language • Based on EXPRESSION • Cycle-accurate simulation • Instruction set information -> Instruction cycles • Structure information -> pipeline stages • Can’t describe interrupt behaviors • Extensions – Exception Description • Instruction’s relationship with external interrupt • Vector address • Trigger time : legal interrupt arrival time • Action time : when the microprocessor responses • Etc …

Automatic External Interrupt HW/SW Generation Assertion rule data base Automatic External Interrupt HW/SW Generation

Fetch Execute2 Decode Execute1 Execute3 FIQ IRQ FIQ FIQ Dabort IRQ IRQ Pabort Mem. access Individual Interrupts • Only one external interrupt arrives before the microprocessor accepts another one For (each interrupt source i) for( each instruction j in processor’s instruction-set) { for( every cycle k of the instruction j) generate a test case to trigger interrupt i at k cycle of instruction j } 8 individual interrupt for load instruction Load

Dabort IRQ IRQ IRQ FIQ FIQ FIQ Pabort Fetch Execute2 Decode Execute1 Execute3 FIQ FIQ Dabort IRQ Pabort Mem. access Concurrent interrupts • Multiple external interrupts arrive before the microprocessor responses to any of them For (each instruction j in processor’s instruction set) { Find out the legal time slot of instruction j for all external interrupt Select 2..n external interrupts to trigger For( each combination) generate a test case to trigger interrupt i and i+1 and ...n while executing instruction j } Load

Graph Model for Nested Interrupts • The microprocessor can accept another external interrupt when executing the interrupt service routine caused by a previous interrupt • State : microprocessor’s mode • Directed edge : legal mode transition from predecessor state to successor state • Path : A legal nested interrupt mode transition • Depth-First-Search to find all cases One nested interrupt case ARM7 PIC16

Verification environment Automatic External Interrupt HW/SW Generation

IRQ Load RTN. addr. INT. Vector Exe.3 SRV. Exe.2 Fetch Decode Exe.1 n cycles Automatic verification mechanism Match T= 2 1 Trigger Verify Verify 1 Match A= Wait 2 3 4 5 IRQ Instruction address Software trigger

Summary of Generated Test Cases • Microprocessor under verify : ARM7 • SUN Blade 2000 workstation • Every case takes 20 cycles on average to complete • More cases can be verified • Automatically

Verification hardware • Simple hardware • Good for FPGA and chip

Bugs found • Branch instruction ignores interrupt • Individual interrupt • The return address of an interrupted 2-cycle MOV instruction is wrong • Individual interrupt • Latency in external interrupt • Individual interrupt

Conclusion • An architecture description language extension is proposed • A CAD tool is proposed to verify the interrupt behaviorof processors • Automatically generate the hardware and software for verification • Automatically verify the processor • The generated hardware is very small • Highly focused verification cases • Less simulation cycles • 4329 verification cases • Less than 88000cycles of RTL simulation • 424 seconds in real time