Is Built-In Logic Redundancy Ready for Prime Time?

390 likes | 486 Vues

This article explores the economic viability of Built-In Logic Redundancy (BILR) for System-on-Chips (SoCs) and provides a cost model comparison. It delves into yield improvement, area overhead analysis, and cost parameters related to implementing BILR in semiconductor designs.

Is Built-In Logic Redundancy Ready for Prime Time?

E N D

Presentation Transcript

Is Built-In Logic Redundancy Ready for Prime Time? Chris Allsup Synopsys, Inc. allsup@synopsys.com March 23, 2010

Trends • Yields declining for each new process… • Longer time to reach maturity • Fewer design starts at a given time after introduction • Increasing adoption of DFM and design-centric yield analysis solutions

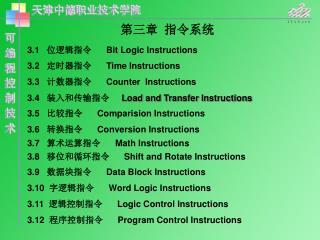

Can Built-In Redundancy Help? * International Technology Roadmap for Semiconductors, System Drivers, 2007 Edition • ITRS predicts* “use of redundancy and reconfigurability to compensate for yield loss will increase” • Designers have used build-in redundancy in: • Aerospace designs • Embedded memories • Multiprocessor designs

Pertinent Questions Is BILR economically viable for most SoCs? If so, under what conditions? What is the most cost-effective approach?

Approach i • Cost Model Not Verified in Silicon Construct cost model that estimates total cost to manufacture, test, and package one functional part Consider only costs most sensitive to implementing BILR Compare total BILR cost with baseline

Example: Blocks A and B Each Have 2-Fold Redundancy Design with Built-in Redundant Logic A' B' Original Design B A B A Part fails Part functions i • Yield Improves Even at Higher Defect Density

Example BILR ArchitectureBlocks Have 3-Fold Redundancy (n=3) VDD 2 3 2 3 1 1 BILR Control Block Fail_Test Start_Test Tester

BILR Design Parameters n n … … … … … … … … 2 2 αA α1A α2A αNA Target BILR 1 1 1 2 N A (1-α)A Fraction of die area targeted for redundancy (α) Redundancy level (n) Number of blocks (N) targeted for redundancy each with fractional area αjAα1 + …+ αN= α

Area Overhead of Control Block • Total across blocks: φA = (φ0 + φ1nN)·A • State machines, counters, status registers, decoders, fuse or anti-fuse elements for repair • Area overhead not specific to each targeted block represented by fractional die size φ0A • Area overhead specific to each targeted block but independent of block size and represented by fractional die size φ1n·A

Area Overhead of “Configuration”Blocks A and B Each Have 3-Fold Redundancy Block A Block B OE1_A IE1_B OE2_A IE2_B OE3_A IE3_B

Area Overhead of “Configuration” • β = β0 + β1N + β2N2 • I/O multiplexing logic, interconnect, power switches dependent on block size • Expressed as fraction β of the area overhead for each targeted block. Each block has area overhead nβαjA • βincreases with number of blocks targeted for redundancy

Area Overhead of BILR Logic=(φ+nβα)A n n … … … … … … … … 2 2 α1A α2A αNA 1 1 1 2 N A

Area Overhead of BILR Logic=(φ+nβα)A • Area φAof control block – independent of block size φA … n … … … … βα1A βα2A βαNA 2 … αA α1A α2A αNA 1 1 2 N (1-α)A A • AreanβαA of “configuration” – dependent on block size

Area Overhead of BILRα =1, n =2, φ, βIncrease Linearly • Total % area overhead of BILR logic = φ + nβα

Expected Yield Y1 Y2 YN Yield is product of the yields of each sub-system: n Y´ = Y(1- α)A·Y1 ·Y2…YN ·YφA … … Yj = Pr {at least 1 fold functional} = 1 Pr {all folds fail} 2 α2A αNA α1A 1 Y(1-α )A (1-α)A

Yield Model and Parameters i • Yield Model and Parameters Should be Accurate • Macro yield models vary based on shape of PDF • Uniform, delta, triangular, exponential, etc. • For this analysis, assume defects behave as random point defects • Defects Poisson-distributed • Yield parameters • Circuit area (cm2) • Defect density D0 (defects/cm2)

Cost Model i • Timing and Power Impact Not “Expensed” • Estimates direct costs ($/good die) most sensitive to BILR: • Fabrication cost • Test execution cost • Packaging cost • Test escape cost Ctotal = Cfab + Cexec + Cpac + Cesc

Fabrication Cost Cs = die area cost multiplier for fabrication ($/cm2) A´ = BILR die size (cm2) Y´ = BILR yield Cost to manufacture each good die:

Test Execution Cost • High volume production • BILR does not add new steps or incur additional cost • Repair already in use for embedded memories • Tester hardware costs >> non-tester hardware costs such as probe cost and repair station cost • Test time per part after BILR programming virtually same as baseline

Test Execution Cost R = tester execution time cost ($/sec) T´= BILR test time per die (sec) Y´ = BILR yield Cost per good die to execute manufacturing tests at wafer probe:

Baseline Test Architecture 1 2 M …… …… Same scan inputs fan-in to all blocks Scan outputs of each block muxed at top level Blocks tested in succession

BILR Test Architecture … … 1 2 N N+1 M … … n n n … … Same scan inputs fan-in to all blocks Scan outputs of each block muxed at top level Blocks tested in succession

Packaging Cost Cpacb= packaging cost of baseline design ($/good die) 𝜇pac = packaging multiplier Packaging cost per good die is weakly correlated with die area, though it could increase if die size increases substantially Assume uplift εsuch that Cpac = Cpacb [ 1+ 𝜇pac · εα(n-1) ]

Packaging Cost: 30% Uplift Cpacb=$5.00/good_die, µpac = 1

Test Escape Cost * S. Wei, et al. “To DFT or Not To DFT?”, ITC 1997, pp. 557-566 Cost per good die to fabricate, test and package defective parts* Cesc = 𝜇esc · (Cfab + Cexec + Cpac) · E Escape rate E is ratio of defective parts that pass tests to total number of passing parts Model predicts slightly lower escape rate for BILR design since all configuration logic must be fully functional

Total Cost vs. Defect Density α =1, n =2, N=20 A=1.0 cm2, T=2.0 sec, Cs=$4.00/cm2, R=$0.06/sec, Cpack =$5.00/good_die,ε=30%, µpack=1, f=99.9%, µesc =20,β0 =2%,β1 =0.2%,β2 =0,φ0 =2%,φ1 =0.2%. Baseline BILR

M, N Parameter SweepD0 = 1.0, n=2 A=1.0 cm2, T=2.0 sec, Cs=$4.00/cm2, R=$0.06/sec, Cpacb =$5.00/good_die,ε=30%, µpac=1, f=99.9%, µesc =20,β0 =2%,β1 =0.2%,β2 =0,φ0 =2%,φ1 =0.2%. Number of Total Blocks (M)

M, N Parameter Sweep D0 = 2.0, n=2 A=1.0 cm2, T=2.0 sec, Cs=$4.00/cm2, R=$0.06/sec, Cpacb =$5.00/good_die,ε=30%, µpac=1, f=99.9%, µesc =20,β0 =2%,β1 =0.2%,β2 =0,φ0 =2%,φ1 =0.2%. Number of Total Blocks (M)

M, N Parameter Sweep D0 = 3.0, n=2 A=1.0 cm2, T=2.0 sec, Cs=$4.00/cm2, R=$0.06/sec, Cpacb =$5.00/good_die,ε=30%, µpac=1, f=99.9%, µesc =20,β0 =2%,β1 =0.2%,β2 =0,φ0 =2%,φ1 =0.2%. Number of Total Blocks (M)

M, N Parameter Sweep D0 = 3.0, n=3 A=1.0 cm2, T=2.0 sec, Cs=$4.00/cm2, R=$0.06/sec, Cpacb =$5.00/good_die,ε=30%, µpac=1, f=99.9%, µesc =20,β0 =2%,β1 =0.2%,β2 =0,φ0 =2%,φ1 =0.2%. Number of Total Blocks (M)

Is BILR Cost-Effective for SoCs? Total Cost • Not if defect density low • If defect density is high, it depends on: • BILR design and test parameters • Cost infrastructure • Area overhead of BILR

BILR Guidelines Yield Increasing block granularity increases yield, decreases cost, up to a point Increasing redundancy above n=2 not as cost-effective

What is Most Cost-Effective Approach? Total Cost i • Thank You! Divide design into N blocks with 2-fold redundancy N corresponds to minimum cost point