ALCT/TMB/RAT Test Stand at CERN

60 likes | 195 Vues

The ALCT-TMB-RAT test stand is being set up at CERN, with initial configurations underway. Today's tasks include setting up the computer and crate controller. David Saltzberg will be bringing additional equipment on Sunday. The aim is to have everything ready by Monday after minor adjustments. In parallel, there is an effort to adapt UCLA TMB test software into the emuLib system, focusing on minimal code rewriting. Meanwhile, Joe and Indara are investigating fundamental muonic timing issues that could be related to software and firmware interactions. Comprehensive testing continues to ensure optimal functionality.

ALCT/TMB/RAT Test Stand at CERN

E N D

Presentation Transcript

ALCT/TMB/RAT Test Stand at CERN • Setting up complete duplicate of the ALCT-TMB-RAT test stand at CERN. • Setting up computer, crate controller today. • David Saltzberg is coming to CERN on Sunday with the remaining equipment. • Just need to plug in some things, move rails around on the rear of the crate (to accommodate RAT board)---Should be done by Monday if things go okay.

UCLA TMB Test Software • Discussed with Karoly and Jinghua about the best approach to adapting the UCLA TMB test software • Both were very much in favor of extracting and porting selected components of the software into the emuLib system. Shouldn’t be a problem.. • Hoping to do a very simple port, leaving the UCLA code mostly as-is.. Write a wrapper around needed emulib functions and minimize having to rewrite code. • Right now removing Microsoft Visual C++ components of the software and rewriting with standard C++ libraries. • Starting to work out a basic framework for porting the code.. Identifying what needs to be translated, finding emuLib equivalents. • Starting with muon injection code. Can work on other tools if they’re wanted

Muonic timing • Working with Indara, Jason on investigating the problems with ALCT muonic timing. • Issues are more fundamental than just muonic timing.. ALCT-tx windows aren’t being found, muonic timing capabilities have been cannibalized to compensate for this. • Likely conflated issues of software + firmware. Two cases.. maybe related: • 1D-Tx and 1D-Rx window are both found, but the 2D scan fails to find any good spots for certain TOFs. This is a feature of more recent software versions, possibly related to pipeline depth scan. Right now comparing two versions (working + nonworking) of code to track down what change introduced this. Indara reports that in these cases, a good working window can found based on the 1D scans, despite the 2D scan failing.. • No 1D-Tx window is found for certain TOFs. • Firmware? Firmware+software interaction? • Will keep testing..

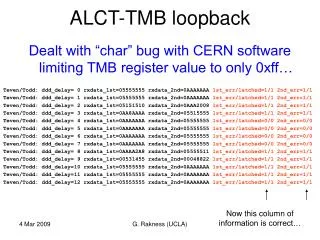

vme_tst_v7 Main Menu 21: Sequencer State/Seq Debug/Buffer Queue/L1A Queue 22: MPC Accept 23: ALCT+CFEB Loopback Tests 24: Boot Register Test 25: RAT Automatic full test: Requires TMB+backplane 26: Scope snapshot of current system 27: Trim Vcore or Vtt 28: TMB Unjam, try to clear a jammed TMB 29: Program Xilinx PROMs 30: JTAG PROM file utilities 31: VME PROM file utilities 32: Check U76 JTAG Bus-Hold circuit 33: VME register dump/compare 34: Load VME registers from dump file 35: Playback event dump to display header and raw hits 36: Playback event dump into TMB, compare result 37: Read/Write Phaser Delays 38: Fire VME sysreset 39: VME bus contention test 40: GTX Optical Receiver Status 1: TMB Slot [%2.2i] adr=%6.6X\n",islot,base_adr); 2: Read ID Register 3: Read Boot Register 4: Peek/Poke Address 5: Read Trigger/Error/Discard counters 6: Read/Write 3D3444 Delays with State Machine 7: Hard Reset TMB 8: Hard Reset ALCT 9: Read DMB Raw Hits RAM 10: Walking 1 Tests 11: Read ADC+Status Register 12: Read FPGA and User PROM IDcodes+RAT 13: Read Hardware Serial Numbers 14: Crate Scan 15: Read Loopback Backplane JTAG Chain 16: Trigger Tests 17: MPC Tests 18: TMB Automatic full test: Loop-back backplane 19: RAT Tests 20: TTC Command/FMM Status

Submenu 16: Trigger Tests TMB Trigger Test Menu: 1: Inject ALCT 2: Inject CLCT 3: Inject ALCT+CLCT 4: Inject ALCT+CLCT + readout 5: Fire ext_trig + L1A to ALCT + readout ALCT RAM 6: Fire CLCT ext trig linked with ALCT ext trig 7: Fire CLCT pattern injector, check CLCT0 8: External trigger ALCT+CLCT 9: External trigger ALCT 10: External trigger CLCT 11: extTrig ALCT+CLCT with GTL pulser 12: extTrig ALCT+CLCT with GTL pulser check CRC 13: Check bxn reset and increment 14: Fire L1A-only event. check readout 15: Fire VME trigger + readout