SVT Trigger Database and Related Hardware Memories

70 likes | 176 Vues

Explore SVT's trigger database and hardware memories for efficient performance. Learn about FPGA programs, storage options, and necessary modifications for changing beam conditions.

SVT Trigger Database and Related Hardware Memories

E N D

Presentation Transcript

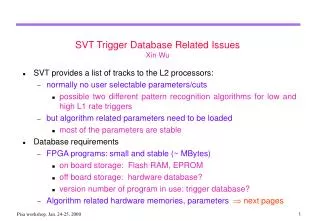

SVT Trigger Database Related IssuesXin Wu • SVT provides a list of tracks to the L2 processors: • normally no user selectable parameters/cuts • possible two different pattern recognition algorithms for low and high L1 rate triggers • but algorithm related parameters need to be loaded • most of the parameters are stable • Database requirements • FPGA programs: small and stable (~ MBytes) • on board storage: Flash RAM, EPROM • off board storage: hardware database? • version number of program in use: trigger database? • Algorithm related hardware memories, parameters next pages

Algorithm Related Hardware Memories and Parameters • Affect trigger performance (efficiency and fake rate) • some need to be modified when beam conditions change • no experience yet, to be seen! • should be accessible also by offline (Trigsim++) • Therefore belong to the Trigger Database (actual files or pointers) • Hardware memories on SVT boards • 36 Hit Finders: PEDRAM, CRAM • 12 Hit Buffers : SSMAP, AMMAP • 12 AM Sequencers (12): SSMAP, Seq_RAM • 24 AM Boards: AM_patterns • 12 Track Fitters: SS_MAP, MAKE_ADDR, P0RAM, COERAM, CHI2_RAM

Hit Finder Hardware Memories and Parameters • PED_RAM: pedestals and thresholds • ALTERA chip internal SRAM • channel pedestal: 7-bit, 1K10 streams/board 360 KB total • chip threshold and cluster charge cut: 3Byte/chip 8.4 KB total • max # of clusters: 1 Byte/stream 360 Bytes total • # of chips: 1 Byte/stream 360 Bytes total • CRAM: look-up table for cluster finding • Static RAM • 6 bits, 32K 10 streams, same for all boards 320 KB total • Stream number to barrel/layer map • ALTERA chip internal SRAM • 6 bits, 10 Byte/board 360 Bytes total

HB/AMS/AMB Hardware Memories and Parameters • SSMAP (hb): hit to super-strip look-up table • DRAM • 15-bit, 128K/board 3 MB total • AMMAP (hb): road to Super-Strip list look-up table • DRAM • 16-bit, 1 M/board 24 MB total • SSMAP (ams): same as SSMAP of hb • Seq_RAM (ams): microsequencer RAM • DRAM • 24-bit, 128k/board, same for all boards 512 KB total • maxRoad and empty layer register (ams): • 12-bit register 2 B total • AM_patterns (amb): AM patterns • AM chips: 128 chips/board, 128 patterns/chip • 12-bit, 6 /pattern 192 KB/board 4.5 MB total

Track Fitter Hardware Memories and Parameters • SS_MAP: edge positions of super-strips in a road • DRAM • 24-bit, 32K/board 1.125 MB total • MAKE_ADDR: map to appropriate fitting parameters • DRAM • 13-bit, 16K/board 384 KB total • P0RAM(intercept memory): track parameters at the edge position • Flash Ram • 14-bit, 6M/board 144 MB total • COERAM (coefficient memory): coefficients of multiplication • ALTERA chip internal SRAM • 67-bit, 900/board 95 KB total • CHI2_RAM (2memory): look-up table to calculate the square of • ALTERA chip internal SRAM • 10-bit, 64/board, same for all boards 128 Bytes total

Track Fitter Hardware Memories and Parameters (Cont.) • Shift control registers: control shifting distance after multiplications • 15-bit, 6/board, same for all boards 12 Bytes total • cuts registers: cut on fitted 1, 2, 3 • 17-bit, 1/board, same for all boards 3 Byte total

Summary • Need large disk space to store hardware memory files • P0RAM (144 MB), AMMAP(24MB), AM_pattern(4.5MB), SSMAP(3MB) ~ 200MB • No frequent change necessary, if beam stable! • but version numbers should be recorded for each run for offline use • Amount of down loading at run start-up is less • Hit Finder and Track Fitter have Flash RAMs and Static RAMs • need to down load: • AMMAP(24MB), AM_pattern(4.5MB), SSMAP(3MB), ... ~ 40MB • The details of the SVT database related issues will be discussed at a workshop in Pisa next week WE WILL BE BACK!