Logic Families

Logic Families. Logic Family : A collection of different IC’s that have similar circuit characteristics The circuit design of the basic gate of each logic family is the same The most important parameters for evaluating and comparing logic families include : Logic Levels Power Dissipation

Logic Families

E N D

Presentation Transcript

Logic Families • Logic Family : A collection of different IC’s that have similar circuit characteristics • The circuit design of the basic gate of each logic family is the same • The most important parameters for evaluating and comparing logic families include : • Logic Levels • Power Dissipation • Propagation delay • Noise margin • Fan-out ( loading )

the most important to understand Example Logic Families • General comparison or three commonly available logic families.

Implementing Logic Circuits • There are several varieties of transistors – the building blocks of logic gates – the most important are: • BJT (bipolar junction transistors) • one of the first to be invented • FET (field effect transistors) • especially Metal-Oxide Semiconductor types (MOSFET’s) • MOSFET’s are of two types: NMOS and PMOS

Transistor Size Scaling Performance improves as size is decreased: shorter switching time, lower power consumption. 2 orders of magnitude reduction in transistor size in 30 years.

Moore’s Law • In 1965, Gordon Moore predicted that the number of transistors that can be integrated on a die would double every 18 to 14 months • i.e., grow exponentially with time • Considered a visionary – million transistor/chip barrier was crossed in the 1980’s • 2300 transistors, 1 MHz clock (Intel 4004/4040) - 1971 • 42 Million transistors, 2 GHz clock (Intel P4) - 2001 • 140 Million transistors, (HP PA-8500)

Moore’s Law and Intel From Intel’s 4040 (2300 transistors) to Pentium II (7,500,000 transistors) and beyond

TTL and CMOS • Connecting BJT’s together gives rise to a family of logic gates known as TTL • Connecting NMOS and PMOS transistors together gives rise to the CMOS family of logic gates BJT MOSFET (NMOS, PMOS) transistor types CMOS TTL logic gate families

Electrical Parameters And Interpretation Of Data Sheets • Voltages and Currents • Noise Margin • Power Dissipation • Propagation Delay • Speed-Power Product • Fan-In, Fan-Out • Comparison of Logic Families • Interpretation of Data Sheets

TTL faster (some versions) strong drive capability rugged CMOS lower power consumption simpler to make greater packing density better noise immunity Electrical Characteristics • Complex IC’s contain many millions of transistors • If constructed entirely from TTL type gates would melt • A combination of technologies (families) may be used • CMOS has become most popular and has had greatest development

Voltage & Current • For a High-state gate driving a second gate, we define: • VOH (min), high-level output voltage, the minimum voltage level that a logic gate will produce as a logic 1 output. • VIH (min), high-level input voltage, the minimum voltage level that a logic gate will recognize as a logic 1 input. Voltage below this level will not be accepted as high. • IOH, high-level output current, current that flows from an output in the logic 1 state under specified load conditions. • IIH, high-level input current, current that flows into an input when a logic 1 voltage is applied to that input. Test setup for measuring values

Voltage & Current • For a Low-state gate driving a second gate, we define: • VOL (max), low-level output voltage, the maximum voltage level that a logic gate will produce as a logic 0 output. • VIL (max), low-level input voltage, the maximum voltage level that a logic gate will recognize as a logic 0 input. Voltage above this value will not be accepted as low. • IOL , low-level output current, current that flows from an output in the logic 0 state under specified load conditions. • IIL , low-level input current, current that flows into an input when a logic 0 voltage is applied to that input. I I OL IL Inputs are connected to Vcc instead of Ground V V OL IL Ground

logic 1 indeterminate input voltage logic 0 Electrical Characteristics • Important characteristics are: • VOHmin min value of output recognized as a ‘1’ • VIHmin min value input recognized as a ‘1’ • VILmax max value of input recognized as a ‘0’ • VOLmax max value of output recognized as a ‘0’ • Values outside the given range are not allowed.

5.0V 5.0V Logic 1 Logic 1 3.5V 2.5V Indeterminate Indeterminate 1.5V • 0.8V Logic 0 Logic 0 0V 0V CMOS TTL Logic Level & Voltage Range • Typical acceptable voltage ranges for positive logic 1 and logic 0 are shown below • A logic gate with an input at a voltage level within the ‘indeterminate’ range will produce an unpredictable output level.

logic 1 indeterminate input voltage logic 0 Noise Margin • If noise in the circuit is high enough it can push a logic 0 up or drop a logic 1 down into the indeterminate or “illegal” region • The magnitude of the voltage required to reach this level is the noise margin • Noise margin for logic high is: • NMH = VOHmin – VIHmin VOHmin VIHmin VILmax VOLmax

Noise Margin • Difference between the worst case output voltage of one stage and worst case input voltage of next stage • Greater the difference, the more unwanted signal that can be added without causing incorrect gate operation NMhigh = VOHmin - VIHmin NMlow = VILmax - VOLmax

Worked Example • Given the following parameters, calculate the noise margin of 74LS series. Solution: High Level Noise Margin, VNH = VOH (min) - VIH (min)=2.7V-2.0V=0.7V Low Level Noise Margin, VNL = VIL (max) - VOL (max)=0.8V-0.4V=0.4V

Noise Margin & Noise Immunity • Noise immunity of a logic circuit refers to the circuit’s ability to tolerate noise voltages on its inputs. • A quantitative measure of noise immunity is called noise margin • High Level Noise Margin, VNH = VOH (min) - VIH (min) • Low Level Noise Margin, VNL = VIL (max) - VOL (max) Logic 1 Logic 1 VOH (min) VNH VIH (min) VIL (max) VNL VOL (max) Logic 0 Logic 0 Input Voltage Ranges Output Voltage Ranges

Further Important Characteristics • The propagation delay (tpd) which is the time taken for a change at the input to appear at the output • The fan-out, which is the maximum number of inputs that can be driven successfully to either logic level before the output becomes invalid

Speed: Rise & Fall Times • Rise Time • Time from 10% to 90% of signal, Low to High • Fall Time • Time from 90% to 10% of signal, High to Low rise time fall time 10% 90% 90% 10%

Input 50% 0 Output 0 tPHL tPLH Speed: Propagation Delay • A logic gate always takes some time to change states • tPLH is the delay time before output changes from low to high • tPHL is the delay time before output changes from high to low • both tPLH & tPHL are measured between the 50% points on the input and output transitions

Power Dissipation • Static • I2R losses due to passive components, no input signal • Dynamic • I2R losses due to charging and discharging capacitances through resistances, due to input signal

Speed-Power Product • Speed (propagation delay) and power consumption are the two most important performance parameters of a digital IC. • A simple means for measuring and comparing the overall performance of an IC family is the speed-power product (the smaller, the better). • For example, an IC has • an average propagation delay of 10 ns • an average power dissipation of 5 mW • the speed-power product = (10 ns) x (5 mW) = 50 picoJoules (pJ)

Logic Family Tradeoffs • Looking for the best speed/power product • tp and Pd are normally included in the data sheet for each device • Older logic families are the worst • CMOS is one of the best • FPGAs use CMOS

TTL - Example SN74LS00 • Recommended operating conditions • Vcc supply voltage 5V ± 0.5 V • input voltages VIH = 2V VIL = 0.8V • Electrical Characteristics • output voltage VOH = 2.7V (worst case) VOL = 0.5V • max input currents IIH = 20µA IIL = -0.4mA • propagation delay tpd = 15 nS • noise margins for a logic 0 = 0.3V for a logic 1 = 0.7V • Fan-out 20 TTL loads 5 Volt Input Range for 1 Output Range for 1 2.7 2.0 0.8 Input Range for 0 Output Range for 0 0.5 0 Volt

Fan-In • Number of input signals to a gate • Not an electrical property • Function of the manufacturing process NAND gate with a Fan-in of 8

Fan-Out • A measure of the ability of the output of one gate to drive the input(s) of subsequent gates • Usually specified as standard loads within a single family • e.g., an input to an inverter in the same family • May have to compute based on current drive requirements when mixing families • Although mixing families is not usually recommended

VOH Low IIH VOL High IIL Current Sourcing and Sinking • Current-source : the driving gate produces a outgoing current • Current-sinking : the driving gate receives an incoming current

Fan-Out • An illustration of fan-out and the associated source and sink currents

Worked Example • How many 74LS00 NAND gate inputs can be driven by a 74LS00 NAND gate outputs ? Solution: Refer to data sheet of 74LS00, the maximum values of IOH = 0.4mA, IOL= 8mA, IIH= 20uA, and IIL= 0.4mA Hence, fan-out(high) = IOH(max) / IIH(max)=0.4mA/20uA=20 fan-out(low) = IOL(max) / IIL(max)=8mA/0.4mA=20, the overall fan-out = fan-out(high) or fan-out(low) whichever is lower. Hence, overall fan-out = 20

Gate Drive Capability: Fan-Out • A logic gate can supply a maximum output current • IOH(max), in the high state or • IOL(max), in the low state • A logic gate requires a maximum input current • IIH(max), in the high state or • IIL(max), in the low state • Ratio of output and input current decide how many logic gates can be driven by a logic gate • fan-out(high) = IOH(max) / IIH (max) • fan-out(low) = IOL(max) / IIL(max) • overall fan-out = fan-out(high) or fan-out(low) whichever is lower • A typical figure of fan-out is ten (10)

Wired-AND • Open collector outputs connected together to a common pull-up resistor • Any collector can pull the signal line low • Logically an AND gate

Tri-State Logic • Both output transistors of totem-pole output are turned off • Usually used to bus multiple signals on the same wire • Gates not enabled present high-Z to bus and therefore do not interfere with other gates putting signals on the bus

Tri-State Logic • Tri-state logic includes a switch at the output • In the figure below, the three states are illustrated: • Logic High output • Logic Low output • High impedance (Hi-Z) output

Electronic Combinational Logic • Within each of these families there is a large variety of different devices • We can break these into groups based on the number gates per device

SSI Devices • Each package contains a code identifying the package N74LS00 Manufacturers Code N = National Semiconductors SN = Signetics Family L LS H Member 00 = Quad 2 input NAND 02 = Quad 2 input Nor 04 = Hex Invertors 20 = Dual 4 Input NAND Specification

7400 Series History • 1960s space program drove development of 7400 series • Consumed all available devices for internal flight computer • $1000 / device (1960 dollars) • 10:1 integration improvement over discrete transistors • 1963 Minuteman missile forced 7400 into mass production • Drove pricing down to $25 / circuit (1963 dollars)

7400 Series Evolution • BJT storage time reduction by using a BC Schottky diode. • Schottky diode has a Vfw=0.25V. When BC junction becomes forward biased Schottky diode will bypass base current. C B

Characteristics: TTL and MOS • TTL stands for Transistor-Transistor Logic • uses BJTs • MOS stands for Metal Oxide Semiconductor • uses FETs • MOS can be classified into three sub-families: • PMOS (P-channel) • NMOS (N-channel) • CMOS (Complementary MOS, most common) Remember:

TTL Circuit Operation Table explaining the operation of the TTL NAND gate circuit A standard TTL NAND gate circuit

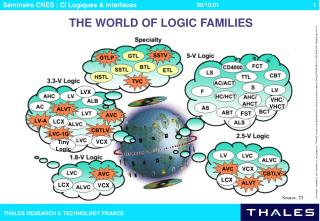

Transistor-Transistor Logic Families • Transistor-Transistor Logic Families: • 74L Low power • 74H High speed • 74S Schottky • 74LS Low power Schottky • 74AS Advanced Schottky • 74ALS Advance Low power Schottky

MOS Circuit Operation Table explaining the operation of the CMOS inverter circuit A CMOS inverter circuit

CMOS Logic Families • CMOS Logic Families • 40xx/45xx Metal-gate CMOS • 74C TTL-compatible CMOS • 74HC High speed CMOS • 74ACT Advanced CMOS -TTL compatible

CMOS Family Evolution • CMOS Logic Trend: Reduction of dynamic losses (cross-conduction, capacitive charge/discharge cycles) by decreasing supply voltages: • 12V→5V →3.3V →2.5V → 1.8V → 1.5V … • Reduction of IC power dissipation is the key to: • lower cost (packaging) • higher integration • improved reliability