Exploring Parallel Data Rate Solutions and Modularity Challenges in High-Speed Driver Designs

10 likes | 119 Vues

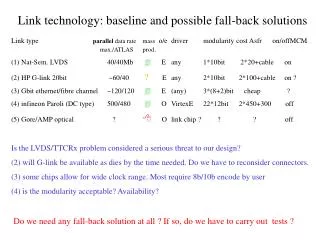

This document examines baseline and potential fallback solutions for parallel data rate connections in advanced driver designs. It addresses modularity, cost considerations, and specific technologies like LVDS, G-link, and ethernet options. Key concerns discussed include the availability of these technologies, the necessity for wide clock range compatibility, and the implications of 8b/10b encoding requirements. Further, it questions whether the LVDS/TTCRx problem poses a significant risk to design integrity, and evaluates the need for testing and fallback strategies within the project timeline.

Exploring Parallel Data Rate Solutions and Modularity Challenges in High-Speed Driver Designs

E N D

Presentation Transcript

Link technology: baseline and possible fall-back solutions Link type parallel data rate mass o/e driver modularity cost Asfr on/offMCM max./ATLASprod. (1) Nat-Sem. LVDS 40/40Mb E any 1*10bit 2*20+cable on (2) HP G-link 20bit ~60/40 ?Eany 2*10bit2*100+cable on ? (3) Gbit ethernet/fibre channel ~120/120 E(any) 3*(8+2)bitcheap ? (4) infineon Paroli (DC type) 500/480 OVirtexE 22*12bit2*450+300 off (5) Gore/AMP optical ? Olink chip ? ? ? off Is the LVDS/TTCRx problem considered a serious threat to our design? (2) will G-link be available as dies by the time needed. Do we have to reconsider connectors. (3) some chips allow for wide clock range. Most require 8b/10b encode by user (4) is the modularity acceptable? Availability? Do we need any fall-back solution at all ? If so, do we have to carry out tests ?