Combinational Logic

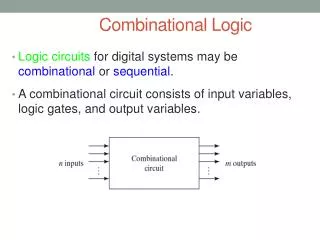

Combinational Logic. Combinational Circuits. Combinational circuit (logic gates). n binary inputs. m binary outputs. n input bits 2 n possible binary input combinations For each possible input combination, there is one possible output value truth table

Combinational Logic

E N D

Presentation Transcript

Combinational Circuits Combinational circuit (logic gates) n binary inputs m binary outputs • n input bits 2n possible binary input combinations • For each possible input combination, there is one possible output value • truth table • Boolean functions (with n input variables) • Examples: adders, subtractors, comparators, decoders, encoders, and multiplexers.

Possible Design Steps • Find out the number of inputs and outputs • Derive the truth table that defines the required relationship between inputs and outputs • Obtain asimplified Boolean function for each output • Draw the logic diagram • Verify the correctness of the design

Example: Design Process • BCD-to-2421 Converter • Verbal specification: • Given a BCD digit (i.e. {0, 1, …, 9}), the circuit computes 2421 code equivalent of the decimal number • Step 1: how many inputs and how many outputs? • four inputs and four outputs • Step 2: • Obtain the truth table • 0000 0000 • 1001 1111 • etc.

BCD-to-2421 Converter • Truth Table

BCD-to-2421 Converter CD AB 00 01 11 10 00 0 0 0 0 01 0 1 1 1 11 10 1 1 • Step 3: Obtain simplified Boolean expression for each output • Output x: x x x x x x x = BD +BC + A

Output y: Boolean Expressions for Outputs • Output z:

Boolean Expressions for Outputs • Step 4: Draw the logic diagram • Output t: t = D x = BC + BD + A y = A + BD’ + BC z = A + B’C + BC’D

Example: Logic Diagram A B x = BC + BD + A C D y = A + BD’ + BC z = A + B’C + BC’D t = D

Example: Verification • Step 5: Check the functional correctness of the logic circuit • Apply all possible input combinations • And check if the circuit generates the correct outputs for each input combinations • For large circuits with many input combinations, this may not be feasible. • Statistical techniques may be used to verify the correctness of large circuits with many input combinations

Design Example • Specification • BCD to Excess-3 code converter • Transforms BCD code for the decimal digits to Excess-3 code for the decimal digits • BCD code words for digits 0 through 9: 4-bit patterns 0000 to 1001, respectively • Excess-3 code words for digits 0 through 9: 4-bit patterns consisting of 3 (binary 0011) added to each BCD code word

Design Example (continued) • Formulation (Find truth table) • Conversion of 4-bit codes can be most easily formulated by a truth table • Variables- BCD: A,B,C,D • Variables- Excess-3 W,X,Y,Z • Don’t Cares- BCD 1010 to 1111

Design Example (continued) C C z y 1 1 1 1 0 1 3 2 0 1 3 2 1 1 1 1 4 5 7 6 4 5 7 6 B B X X X X X X X X 12 13 15 14 12 13 15 14 A A 1 X X 1 X X 8 9 11 10 8 9 11 10 D D D D x C C w 1 1 1 0 1 3 2 0 1 3 2 1 1 1 1 4 5 7 6 4 5 7 6 B B X X X X X X X X 12 13 15 14 12 13 15 14 A A 1 X X 1 1 X X 8 9 11 10 8 9 11 10 D B C B C D D • W = A + BC + BD • X = C + D + B • Y = CD + • Z =

Design Example (continued) A W B X Y C D Z • Technology Mapping

Binary Adder/Subtractor • (Arithmetic) Addition of two binary digits • 0 + 0 = 0, 0 + 1 = 1, 1 + 0 = 1, and 1 + 1 = 10 • The result has two components • the sum (S) • the carry (C) • (Arithmetic) Addition of three binary digits

Half Adder x S y C • Truth table S = x’y + xy’ = x y C = xy HA HA

Full Adder 1/2 • A circuit that performs the arithmetic sum of three bits • Three inputs • Two binary outputs

Full Adder 2/2 • Karnaugh Maps S = xy’z’ + x’y’z + xyz + x’yz’ = ... = ... = x y z C = xy + xz + yz Two level implementation 1st level: three AND gates 2nd level: One OR gate

Full Adder: Hierarchical Realization x HA S HA S y C C C z • Sum • S = x y z • Carry • C = xy + xy’z + x’yz = (xy’ + x’y) z + xy = (x y) z + xy • This allows us to implement a full-adder using two half adders. x y z = S

Full Adder Using Half Adders HA HA x y S C z

Integer Addition 1/2 a0 b0 a1 b1 a2 b2 a3 b3 HA y FA x FA y y FA y x x x C1 C2 C3 C4 C z z z C C C S S S S S0 S1 S2 S3 • Binary adder: • A digital circuit that produces the arithmetic sum of two binary numbers • A = (an-1, an-2, …, a1, a0) • B = (bn-1, bn-2, …, b1, b0) • A simple case: 4-bit binary adder

Integer Addition 2/2 a0 b0 a1 b1 a2 b2 a3 b3 FA y FA x FA y y FA y x x x C0=0 C1 C2 C3 C4 z C z z z C C C S S S S S0 S1 S2 S3 Ripple-carry adder

Unsigned Subtraction • Algorithm: • Subtract the subtrahend N from the minuend M • If no end borrow occurs, then M ³ N, and the result is a non-negative number and correct. • If an end borrow occurs, the N > M and the difference M - N + 2n is subtracted from 2n, and a minus sign is appended to the result. • Examples:

Complements • Two complements: • Diminished Radix Complement of N • (r - 1)’s complement for radix r • 1’s complement for radix 2 • Radix Complement • r’s complement for radix r • 2’s complement in binary • Defined as rn- N

Binary 1's Complement • The one's complement is obtained by complementing each individual bit (bitwise NOT). • 1’s complement of 10111010 is 01000101

Binary 2's Complement • Note the result is the 1's complement plus 1, a fact that can be used in designing hardware

Alternate 2’s Complement Method • Given: an n-bit binary number, beginning at the least significant bit and proceeding upward: • Copy all least significant 0’s • Copy the first 1 • Complement all bits thereafter. • 2’s Complement Example: 10010100 • Copy underlined bits: 100 • and complement bits to the left: 01101100

Subtraction with 2’s Complement • For n-digit, unsigned numbers M and N, find M N in base 2: • Add the 2's complement of the subtrahend N to the minuend M: M + (2n N) = M N + 2n • If M N, the sum produces end carry rn which is discarded; from above, M - N remains. • If M < N, the sum does not produce an end carry and, from above, is equal to 2n ( N M ), the 2's complement of ( N M ). • To obtain the result (N – M) , take the 2's complement of the sum and place a to its left.

Unsigned 2’s Complement Subtraction Example 1 • Find 010101002 – 010000112 01010100 01010100 – 01000011 + 10111101 00010001 • The carry of 1 indicates that no correction of the result is required. 2’s comp 1

Unsigned 2’s Complement Subtraction Example 2 • Find 010000112 – 010101002 01000011 01000011 – 01010100 + 10101100 11101111 00010001 • Result = – (00010001) 2’s comp 0 2’s comp

Signed Integers • Positive numbers and zero can be represented by unsigned n-digit, radix r numbers. We need a representation for negative numbers. • To represent a sign (+ or –) we need exactly one more bit of information (1 binary digit gives 21 = 2 elements which is exactly what is needed). • Since computers use binary numbers, by convention, the most significant bit is interpreted as a sign bit: s an–2 a2a1a0where:s = 0 for Positive numberss = 1 for Negative numbersand ai = 0 or 1 represent the magnitude in some form.

Signed Integer Representations • Signed-Magnitude– here the n – 1 digits are interpreted as a positive magnitude. • Signed-Complement– here the digits are interpreted as the rest of the complement of the number. There are two possibilities here: • Signed 1's Complement • Uses 1's Complement Arithmetic • Signed 2's Complement • Uses 2's Complement Arithmetic

Signed-Magnitude Arithmetic • If the parity of the three signs is 0: 1. Add the magnitudes. 2. Check for overflow (a carry out of the MSB) 3. The sign of the result is the same as the sign of the first operand. • If the parity of the three signs is 1: 1. Subtract the second magnitude from the first. 2. If a borrow occurs: • take the two’s complement of result • and make the result sign the complement of the sign of the first operand. 3. Overflow will never occur.

Sign-Magnitude Arithmetic Examples • Example 1: 0010 +0101 • Example 2: 0010 +1101 • Example 3: 1010- 0101

Signed-Complement Arithmetic • Addition: 1. Add the numbers including the sign bits, discarding a carry out of the sign bits (2's Complement), or using an end-around carry (1's Complement). 2. If the sign bits were the same for both numbers and the sign of the result is different, an overflow has occurred. 3. The sign of the result is computed in step 1. • Subtraction: Form the complement of the number you are subtracting and follow the rules for addition.

Signed 2’s Complement Examples • Example 1: 1101 +0011 • Example 2: 1101-0011

2’s Complement Adder/Subtractor • Subtraction can be done by addition of the 2's Complement. 1. Complement each bit (1's Complement.) 2. Add 1 to the result. • The circuit shown computes A + B and A – B: • For S = 1, subtract,the 2’s complementof B is formed by usingXORs to form the 1’scomp and adding the 1applied to C0. • For S = 0, add, B ispassed throughunchanged

Recall how we do subtraction (2’s complement) X – Y = X + (2n – Y) = X + ~Y + 1 Subtractor x0 y0 x2 x1 y1 x3 y3 y2 logic-1 4-bit adder circuit a3 b3 a2 b2 a1 b1 a0 b0 C4 C0 S3 S0 S1 S2 S3 S0 S1 S2 C4

Overflow • How to detect overflows: • two n-bit numbers • we add them, and result may be an (n+1)-bit number overflow. • Unsigned numbers: • easy • check the carryout. • Signed numbers • more complicated • overflow occurs in addition, when the operands are of the same sign

Examples: Overflows 0 1 0 1 1 0 1 0 1 0 1 1 0 0 0 0 -68 68 1 0 0 1 1 0 1 0 1 0 1 0 0 1 1 1 91 -91 1 0 0 1 0 1 1 0 0 1 1 0 0 1 1 1 • Example 1: 8-bit signed numbers 159 • Example 2: 8-bit signed numbers -159

Detecting Overflows 1 0 1 0 1 0 0 1 1 0 1 1 0 0 0 0 A A 0 1 1 0 0 1 0 1 0 1 1 0 0 1 1 1 B B 0 0 C C 0 1 1 0 0 1 0 1 0 1 0 1 0 1 1 1 S S • Remember we have other variables when adding: • Carries Look at C7and C8 in both cases

Detecting Overflows: Second Method • Observations • Case 1: V = 1 when C7 = 1 and C8 = 0 • Case 2: V = 1 when C7 = 0 and C8 = 1 • V = C7 C8 = 1 • Think about whether this could happen when the operands have different signs. • C7= C8

Multiplication/Division by 2n B B B B 3 2 1 0 0 0 C C C C C C 5 4 3 2 1 0 B B B B 3 2 1 0 0 0 C C C C C C 3 2 1 0 1 2 2 2 (b) • (a) Multiplication by 100 • Shift left by 2 • (b) Division by 100 • Shift right by 2 • Remainderpreserved (a)

Multiplication by a Constant • Multiplication of B(3:0) by 101 • See text Figure 513 (a) for contraction 0 B B B B 0 B B B B 3 2 1 0 3 2 1 0 4-bit Adder Carry Sum output C C C C C C C 6 5 4 3 2 1 0

Binary Multipliers y0 y1 x0 y0 y1 x1 HA HA z0 z2 z1 z3 • Two-bit multiplier