Mobile Computer Special Lecture: Combinational Logic Circuits Overview

This lecture covers combinational circuit concepts, including multiplexers, decoders, adders, design procedures, logic simplifications, and exercises. It explains the synthesis and implementation of combinational logic and includes examples and exercises for practical learning.

Mobile Computer Special Lecture: Combinational Logic Circuits Overview

E N D

Presentation Transcript

Combinational Logic Lecture #6

Combinational Circuit 개요 Multiplexer Decoder Half Adder Full Adder Ripple carry Adder Carry-Lookahead Adder 4-bit Adder 강의순서 모바일컴퓨터특강

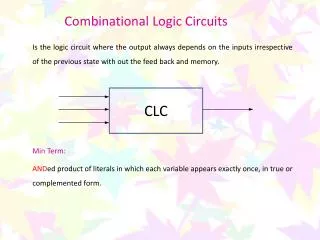

Combinational Logic • One or more digital signal inputs • One or more digital signal outputs • Outputs are only functions of current input values (ideal) plus logic propagation delays i1 Combinational Logic O1 im On 모바일컴퓨터특강

Combinational Logic (cont.) • Combinational logic has no memory • Outputs are only function of current input combination • Nothing is known about past events • Repeating a sequence of inputs always gives the same output sequence • Sequential logic does have memory • Repeating a sequence of inputs can result in an entirely different output sequence 모바일컴퓨터특강

합성(Synthesis) 구현(Implementation) Combinational Logic (cont.) • Design Procedure 회로 기능 명세 서술문 진리표를 이용한 정규논리식 정의 논리식 (Logic Expression) 카르노맵 등을 이용하여 논리식 단순화 최소화된 논리식 (Minimized Logic Expression) 하드웨어 논리회로 모바일컴퓨터특강

Logic simplifications • Consider an automobile buzzer • Buzzer = (Key In and Door Open) or (Headlight On and Door Open) • B = KD + HD = (K+H)D 모바일컴퓨터특강

Simulation • Verify if b_reduced yields the same result. 모바일컴퓨터특강

& : AND ! : NOT # : OR $ : XOR Compilation Report • Verify the reduced equation with Fitter Equation 모바일컴퓨터특강

Floorplan • Verify the reduced equation with Floorplan 모바일컴퓨터특강

Exercise (1) • Simplify X = (ABC’ + B)BC’ by starting with a BDF • Verify the result with compilation report & floorplan 모바일컴퓨터특강

Exercise (2) • Simplify the equations by starting with a VHDL file • X = (AB + (B’+C))’ • Y = (AB)’ + (B+C)’ • Verify the result with compilation report & floorplan 모바일컴퓨터특강

Exercise (3) –Entering a Truth Table with VHDL • Identify the logic with compilation report & floorplan 모바일컴퓨터특강

D0 D1 F D7 S2 S1 S0 MUX (Multiplexer) • 2N data input, • 1 data output, • N control inputs that select one of the data inputs. 모바일컴퓨터특강

Mux 4x1(Signal Assignment, Conditional) library ieee; use ieee.std_logic_1164.all; entity mux41_ when is port( a, b, c, d: in std_logic; s : in std_logic_vector(1 downto 0); y : out std_logic); end mux41_ when; architecture a of mux41_when is BEGIN y <= a when (s=“00”) else b when (s=“01”) else c when (s=“10”) else d; END a; 모바일컴퓨터특강

Mux 4x1(Signal Assignment, Selected) library ieee; use ieee.std_logic_1164.all; entity mux41_with is port( a, b, c, d: in std_logic; s : in std_logic_vector(1 downto 0); y : out std_logic); end mux41_with; architecture a of mux41_with is BEGIN WITH s SELECT y<= a WHEN "00", b WHEN "01", c WHEN "10", d WHEN others; END a; 모바일컴퓨터특강

Mux 4x1 (IF) library ieee; use ieee.std_logic_1164.all; entity mux41_if_proc is port( a,b,c,d : in std_logic; s : in std_logic_vector(1 downto 0); y : out std_logic); end mux41_if_proc; architecture proc of mux41_if_proc is begin process(a,b,c,d,s) begin if( s="00") then y<=a; elsif( s="01") then y<=b; elsif( s="10") then y<=c; else y<=d; end if; end process; end proc; 모바일컴퓨터특강

Mux 4x1 (case) library ieee; use ieee.std_logic_1164.all; entity mux41_case_proc is port( a,b,c,d : in std_logic; s : in std_logic_vector(1 downto 0); y : out std_logic); end mux41_case_proc; architecture proc of mux41_case_proc is begin process(a,b,c,d,s) begin case s is when "00" => y<=a; when "01" => y<=b; when "10" => y<=c; when others => y<=d; end case; end process; end proc; 모바일컴퓨터특강

Decoder3_8.vhd는 미리 작성된 상태임 Mixed Modeling : structure + dataflow Mux 8x1 (Mixed Modeling) Library ieee; Use ieee.std_logic_1164.all; entity mux8_1 is port( a, b, c, d, e, f, g, h : in std_logic; s2, s1, s0 : in std_logic; y : out std_logic); end mux8_1; architecture xxx of mux8_1 is component decoder3_8 port( a, b, c : in std_logic; d0,d1,d2,d3,d4,d5,d6,d7 : out std_logic); end component; signal t : std_logic_vector(7 downto 0); signal d0,d1,d2,d3,d4,d5,d6,d7 : std_logic; begin U1: decoder3_8 port map( s2,s1,s0,d0,d1,d2,d3,d4,d5,d6,d7); t(0) <= a and d0; t(1) <= b and d1; t(2) <= c and d2; t(3) <= d and d3; t(4) <= e and d4; t(5) <= f and d5; t(6) <= g and d6; t(7) <= h and d7; y <= t(0) or t(1) or t(2) or t(3) or t(4) or t(5) or t(6) or t(7); end xxx; t(0) t(1) t(2) t(3) t(4) t(5) t(6) t(7) 모바일컴퓨터특강

같은 표현 sel(2) := s2; sel(1) := s1; sel(0) := s0; Mux 8x1 (Constants) library ieee; use ieee.std_logic_1164.all; entity mux8_1_proc is port( a,b,c,d,e,f,g,h : in std_logic; s2, s1, s0 : in std_logic; y : out std_logic); end mux8_1_proc; architecture proc of mux8_1_proc is constant bits3_0 : std_logic_vector(2 downto 0) := "000"; constant bits3_1 : std_logic_vector(2 downto 0) := "001"; constant bits3_2 : std_logic_vector(2 downto 0) := "010"; constant bits3_3 : std_logic_vector(2 downto 0) := "011"; constant bits3_4 : std_logic_vector(2 downto 0) := "100"; constant bits3_5 : std_logic_vector(2 downto 0) := "101"; constant bits3_6 : std_logic_vector(2 downto 0) := "110"; constant bits3_7 : std_logic_vector(2 downto 0) := "111"; begin process(a,b,c,d,e,f,g,h,s2,s1,s0) variable sel : std_logic_vector(2 downto 0); begin sel := s2 & s1 & s0; case sel is when bits3_0 => y<= a; when bits3_1 => y<= b; when bits3_2 => y<= c; when bits3_3 => y<= d; when bits3_4 => y<= e; when bits3_5 => y<= f; when bits3_6 => y<= g; when others => y<= h; end case; end process; end proc; 모바일컴퓨터특강

Mux 8x1 4bits (Signal Assignment, Selected) library ieee; use ieee.std_logic_1164.all; entity mux81_4bits_with is port( a, b, c, d, e, f, g, h : in std_logic_vector(3 downto 0); s2, s1, s0 : in std_logic; y : out std_logic_vector(3 downto 0) ); end mux81_4bits_with; architecture a of mux81_4bits_with is signal s : std_logic_vector(2 downto 0); BEGIN s <= s2 & s1 & s0; -- s(2)<=s2; s(1)<=s1;s(0)<=s0; WITH s SELECT y <= a WHEN "000", b WHEN "001", c WHEN "010", d WHEN "011", e WHEN "100", f WHEN "101", g WHEN "110", h WHEN others; END a; 모바일컴퓨터특강

Mux 8x1 4bits (case) library ieee; use ieee.std_logic_1164.all; entity mux81_4bits_proc is port( a,b,c,d,e,f,g,h : in std_logic_vector(3 downto 0); s2, s1, s0 : in std_logic; y : out std_logic_vector(3 downto 0)); end mux81_4bits_proc; architecture proc of mux81_4bits_proc is signal sel : std_logic_vector(2 downto 0); begin sel <= s2 & s1 & s0; process(a,b,c,d,e,f,g,h,sel) begin case sel is when "000" => y<= a; when "001" => y<= b; when "010" => y<= c; when "011" => y<= d; when "100" => y<= e; when "101" => y<= f; when "110" => y<= g; when others => y<= h; end case; end process; end proc; 모바일컴퓨터특강

Decoder n • 3-to-8, 4-to–16, n–to–2 M0 M1 M7 A0 A1 A2 A typical 3 – to - 8 decoder circuit 모바일컴퓨터특강

3x8 Decoder (Signal assignment, Conditional) LIBRARY ieee; -- 3x8 decoder using Boolean equations-- USE ieee.std_logic_1164.ALL; ENTITY decoder_a IS PORT(a0,a1,a2 : IN std_logic; y0,y1,y2,y3,y4,y5,y6,y7 : OUT std_logic); END decoder_a ; ARCHITECTURE arc OF decoder_a IS BEGIN y0 <= (NOT a2) AND (NOT a1) AND (NOT a0); y1 <= (NOT a2) AND (NOT a1) AND ( a0); y2 <= (NOT a2) AND ( a1) AND (NOT a0); y3 <= (NOT a2) AND ( a1) AND ( a0); y4 <= ( a2) AND (NOT a1) AND (NOT a0); y5 <= ( a2) AND (NOT a1) AND ( a0); y6 <= ( a2) AND ( a1) AND (NOT a0); y7 <= ( a2) AND ( a1) AND ( a0); END arc; 모바일컴퓨터특강

3x8 Decoder (Signal assignment, Select; Truth Table) LIBRARY ieee; -- 3x8 decoder using vectors USE ieee.std_logic_1164.ALL; -- and selected signal assignment ENTITY decoder_b IS PORT(a : IN STD_LOGIC_VECTOR (2 downto 0); y : OUT STD_LOGIC_VECTOR (7 downto 0)); END decoder_b ; ARCHITECTURE arc OF decoder_b IS BEGIN WITH a SELECT y<="00000001" WHEN "000", "00000010" WHEN "001", "00000100" WHEN "010", "00001000" WHEN "011", "00010000" WHEN "100", "00100000" WHEN "101", "01000000" WHEN "110", "10000000" WHEN "111", "00000000" WHEN others; END arc; 모바일컴퓨터특강

concatenate 3x8 Decoder with enable LIBRARY ieee; -- 3x8 decoder with enable -- USE ieee.std_logic_1164.ALL; ENTITY decoder_c IS PORT(en : IN std_logic; a : IN STD_LOGIC_VECTOR (2 DOWNTO 0); y : OUT STD_LOGIC_VECTOR (7 DOWNTO 0)); END decoder_c ; ARCHITECTURE arc OF decoder_c IS SIGNAL inputs : std_logic_vector(3 DOWNTO 0); BEGIN inputs<=en & a; WITH inputs SELECT y<="00000001" WHEN "1000", "00000010" WHEN "1001", "00000100" WHEN "1010", "00001000" WHEN "1011", "00010000" WHEN "1100", "00100000" WHEN "1101", "01000000" WHEN "1110", "10000000" WHEN "1111", "00000000" WHEN others; END arc; 모바일컴퓨터특강

같은 표현 d(2) <= d2; d(1) <= d1; d(0) <= d0; 3x8 Decoder (CASE) (1) library ieee; use ieee.std_logic_1164.all; entity decoder38_proc is port( d2, d1, d0 : in std_logic; y0,y1,y2,y3,y4,y5,y6,y7 : out std_logic); end decoder38_proc; architecture xxx of decoder38_proc is signal d : std_logic_vector(2 downto 0); signal t : std_logic_vector( 0 to 7); begin d <= d2&d1&d0; process(d) begin case d is when "000" => t<="10000000"; when "001" => t<="01000000"; when "010" => t<="00100000"; when "011" => t<="00010000"; when "100" => t<="00001000"; when "101" => t<="00000100"; when "110" => t<="00000010"; when others => t<="00000001"; end case; end process; y0 <= t(0); y1 <= t(1); y2 <= t(2); y3 <= t(3); y4 <= t(4); y5 <= t(5); y6 <= t(6); y7 <= t(7); end xxx; 회로보다는 설계사양에 관심을 둔 설계방식. 모바일컴퓨터특강

3x8 Decoder (CASE) (2) • Timing Simulation Result 모바일컴퓨터특강

Half Adder (1) • Combinational logic circuits give us many useful devices. • One of the simplest is the half adder, which finds the sum of two bits. • Based on the truth table, we’ll construct the circuit. 모바일컴퓨터특강

Half Adder (2) • The sum can be found using the XOR operation and the carry using the AND operation. • S = X Y, C = XY 모바일컴퓨터특강

Full Adder (1) • Full adder adds carry_in as well. • The truth table for a full adder is shown at the right. 모바일컴퓨터특강

Full Adder (2)- Boolean expression S = m(1,2,4,7) = X’ Y’ Cin + X’ Y Cin’ + X Y’ Cin’ + X Y Cin = X’ (Y’ Cin + Y Cin’) + X (Y’ Cin’ + Y Cin) = X’ (Y Cin) + X (Y Cin)’ = X Y Cin Cout = m(3,5,6,7) = X’ Y Cin + X Y’ Cin + X Y Cin’ + X Y Cin = (X’ Y + X Y’) Cin + XY(Cin’ + Cin) = (X Y) Cin + XY or Cout= XCin+ Y Cin + XY 모바일컴퓨터특강

Full Adder (3) 모바일컴퓨터특강

Full Adder (4) - Dataflow VHDL Description LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY fulladd IS PORT (x, y, cin : INSTD_LOGIC ; s, cout : OUTSTD_LOGIC ); END fulladd ; ARCHITECTURE fulladd_dataflow OF fulladd IS BEGIN s <= x XOR y XOR cin ; cout <= (x AND y) OR (cin AND x) OR (cin AND y) ; END fulladd_dataflow ; 모바일컴퓨터특강

Full Adder (5) – using Half adder 모바일컴퓨터특강

Ripple Carry Adder • Just as we combined half adders to make a full adder, full adders can be connected in series. • The carry bit “ripples” from one adder to the next; hence, this configuration is called a ripple-carryadder. ripple: 잔물결, 파문 Today’s systems employ more efficient adders. 모바일컴퓨터특강

Ripple Carry Adder Operation • All 2n input bits available at the same time • Carries propagate from the FA in position 0 (with inputs x0 and y0) to position i before that position produces correct sum and carry-out bits • Carries ripple through all n FAs before we can claim that the sum outputs are correct and may be used in further calculations 모바일컴퓨터특강

8-bit RC Adder - Structural Description (1) LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY rca_8bit IS PORT (x, y : INSTD_LOGIC_VECTOR(7 DOWNTO 0) ; cin : INSTD_LOGIC ; s : OUTSTD_LOGIC_VECTOR(7 DOWNTO 0) ; cout : OUTSTD_LOGIC ); END rca_8bit ; 모바일컴퓨터특강

8-bit RC Adder - Structural Description (2) ARCHITECTURE structure OF rca_8bit IS component fulladd is port(x, y, cin : IN STD_LOGIC; s, cout : OUT STD_LOGIC); end component; signal C : STD_LOGIC_VECTOR(8 downto 0); BEGIN C(0) <= cin; U0 : fulladd port map(x(0), y(0), C(0), s(0), C(1)); U1 : fulladd port map(x(1), y(1), C(1), s(1), C(2)); U2 : fulladd port map(x(2), y(2), C(2), s(2), C(3)); U3 : fulladd port map(x(3), y(3), C(3), s(3), C(4)); U4 : fulladd port map(x(4), y(4), C(4), s(4), C(5)); U5 : fulladd port map(x(5), y(5), C(5), s(5), C(6)); U6 : fulladd port map(x(6), y(6), C(6), s(6), C(7)); U7 : fulladd port map(x(7), y(7), C(7), s(7), C(8)); cout <= C(8) ; END structure ; 모바일컴퓨터특강

32-bit RC Adder - Structural Description (1) • 생성문(generate statement) 사용 • 규칙적인 구조를 가지는 회로를 반복적으로 생성 • 반복 생성문(for-generate) / 조건 생성문(if-generate) LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY rca_32bit IS PORT (x, y : INSTD_LOGIC_VECTOR(31 DOWNTO 0) ; cin : INSTD_LOGIC ; s : OUTSTD_LOGIC_VECTOR(31 DOWNTO 0) ; cout : OUTSTD_LOGIC; overflow : OUT STD_LOGIC ); END rca_32bit ; 모바일컴퓨터특강

for-generate 문장 Overflow 계산 32-bit RC Adder - Structural Description (2) ARCHITECTURE structure OF rca_32bit IS component fulladd is port(x, y, cin : IN STD_LOGIC; s, cout : OUT STD_LOGIC); end component; signal C : STD_LOGIC_VECTOR(32 downto 0); BEGIN C(0) <= cin; for k in 0 to 31 generate Uk : fulladd port map(x(k), y(k), C(k), s(k), C(k=1)); end generate; cout <= C(32) ; overflow <= C(32) xor C(31); END structure ; 모바일컴퓨터특강

n-bit RC Adder - Dataflow Description (1) • 범용문(Generic statement) 사용 • 회로의 크기 또는 입출력 크기를 매개변수(parameter)에 의해 결정 • entity 또는 component 내에서 선언 • 반드시 port 문장보다 먼저 선언 LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY rca_nbit IS GENERIC( n : integer := 32); PORT (x, y : INSTD_LOGIC_VECTOR(n-1 DOWNTO 0) ; cin : INSTD_LOGIC ; s : OUTSTD_LOGIC_VECTOR(n-1 DOWNTO 0) ; cout : OUTSTD_LOGIC; overflow : OUT STD_LOGIC ); END rca_nbit ; 모바일컴퓨터특강

n-bit RC Adder - Dataflow Description (2) ARCHITECTURE dataflow OF rca_nbit IS BEGIN PROCESS(x, y, cin) variable sum : STD_LOGIC_VECTOR(n-1 downto 0); variable C : STD_LOGIC_VECTOR(n downto 0); variable k : integer; BEGIN C(0) := cin; for k in 0 to n-1 loop sum(k) := x(k) xor y(k) xor C(k); C(k+1) := (x(k) and C(k)) or (y(k) and C(k)) or (x(k) and y(k)); end loop; s <= sum; cout <= C(n) ; overflow <= C(n) xor C(n-1); END PROCESS; END dataflow ; 모바일컴퓨터특강

n-bit RC Adder - Dataflow Description (3) • 예제 : 64-bit Ripple Carry Adder • n-bit RC Adder 회로를 이용하여 64-bit RC Adder를 구현하여라 LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY rca_64bit IS PORT (x, y : INSTD_LOGIC_VECTOR(63 DOWNTO 0) ; cin : INSTD_LOGIC ; s : OUTSTD_LOGIC_VECTOR(63 DOWNTO 0) ; cout : OUTSTD_LOGIC; overflow : OUT STD_LOGIC ); END rca_64bit ; 모바일컴퓨터특강

n-bit RC Adder - Dataflow Description (4) ARCHITECTURE structure OF rca_64bit IS component rca_nbit is generic(n : integer); port (x, y : INSTD_LOGIC_VECTOR(n-1 DOWNTO 0) ; cin : INSTD_LOGIC ; s : OUTSTD_LOGIC_VECTOR(n-1 DOWNTO 0) ; cout, overflow : OUT STD_LOGIC ); end component; BEGIN U0 : rca_nbit generic map(64) port map(x, y, cin s, cout, overflow); END structure ; 모바일컴퓨터특강

Carry Lookahead Adder (1) • Ripple-Carry Adder의 장단점 • 장점 : 구조가 단순하다 • 단점 : 캐리 전파지연(carry propagation delay)으로 인한 늦은 연산 속도 • Carry-Lookahead Adder • 각 비트에서 발생하는 캐리를 미리 계산하는 회로를 부가함으로써 연산 속도를 향상 • 입력 비트 수가 커지면 부가 회로가 복잡해지는 문제점 발생 Hierarchical Carry-Lookahead Adder 모바일컴퓨터특강

Carry Lookahead Adder (2) • Carry-Lookahead Adder 원리 • n-th full adder에서의 sum & carry 논리식 • Carry 논리식의 확장 S = Xn Yn Cn Cn+1 = XnYn + (Xn Yn)Cn = Gn + PnCn where Gn = XnYn : generate function Pn = Xn Yn: propagate function 모든 캐리 비트를 입력 신호를 이용하여 미리 계산 가능 Cn+1 = Gn + PnCn =Gn + Pn(Gn-1 + Pn-1Cn-1) = Gn + PnGn-1 + PnPn-1Cn-1 = Gn + PnGn-1 + PnPn-1Gn-2 + PnPn-1Pn-2Cn-2 … = Gn + PnGn-1 + PnPn-1Gn-2 + … + PnPn-1…P1G0 + PnPn-1Pn-2…P1P0C0 모바일컴퓨터특강

Carry Lookahead Adder (3) • Carry-Lookahead Adder 회로도 Ripple-Carry Adder Carry-Lookahead Adder 모바일컴퓨터특강

Carry Lookahead Adder 설계(1) • CLA Block Diagram 모바일컴퓨터특강

Carry Lookahead Adder 설계(2) • CLA 구현 • CGCPU(Carry-Generate/Carry-Propagate Unit) 설계 LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY cgcpu_uint IS PORT (a, b : INSTD_LOGIC_VECTOR(3 DOWNTO 0) ; g, p : OUTSTD_LOGIC_VECTOR(3 DOWNTO 0)); END cgcpu_unit ; ARCHITECTURE dataflow OF cgcpu_unit IS BEGIN g <= a and b; p <= a xor b; END dataflow ; 모바일컴퓨터특강