Addressing Modes

Addressing Modes The methods used in machine instructions to identify the location of an operand . ITCS 3181 Logic and Computer Systems 2014 B. Wilkinson s lides3.ppt Modification date: March 4, 2014. General details Almost always, one operand is held in a register .

Addressing Modes

E N D

Presentation Transcript

Addressing Modes The methods used in machine instructions to identify the location of an operand. ITCS 3181 Logic and Computer Systems 2014 B. Wilkinson slides3.ppt Modification date: March 4, 2014

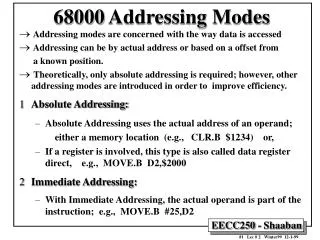

General details Almost always, one operand is held in a register. Addressing mode refers to the other operand. Various addressing modes provided for different purposes. Effective address– the actual address of the operand after all address computations of the addressing mode have been performed. In assembly language, different notations are used to specify addressing mode.

Size of data transfer Memory organized as set of bytes (8 bits). A 32-bit processor would have 32-bit registers. May be several sizes of transfer allowed: 8 bits from memory to least significant 8 bits of register or vice versa. 16 bits from two consecutive memory locations to least significant 16 bits of register or vice versa (uncommon in RISCs) 32 bits from four consecutive memory locations to full 32 bits of register or vice versa.

Size of data transfer Size of transfer needs to be specified. In assembly language, different operation mnemonics or different notations used to specify size of transfer. Example ADD means add 32 bit numbers ADDB means add 8 bit numbers

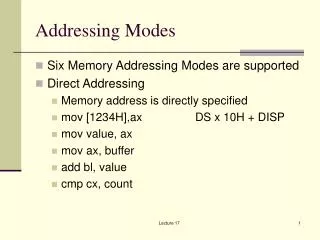

Fundamental Addressing Modes • Direct Addressing (also called Absolute Addressing) • Immediate Addressing • Register (Direct) Addressing • Register Indirect Addressing

Direct (or Absolute) Addressing The operand is in memory and the memory address of the operand is held in instruction: This was the method used to describe instruction formats previously.

Direct (Absolute) Addressing Example LD R2,[100] ;R2=contents of memory, address is 100

Another Direct (Absolute) Addressing Example ST [100], R2 ;memory whose address is 100 = R2 Mnemonic for this instruction may be MOV (move) or ST (store), depending upon the manufacturer’s notation, see later.

Size of data transfer Example LD means load 32 bit number to register ST store 32 bit number to memory LB means load 8 bit number to register SBstore 8 bit number to memory Mnemonic for LD and ST instruction may be MOV (move) depending upon the manufacturer’s notation and size may be indicated in other ways.

Immediate Addressing The operand is held in the instruction:

Immediate Addressing Example MOV R2,123 ;R2 = 123 Useful for constants. For example int x = 123;

Immediate addressing used in compiled code Useful for constants. For example: High level code Assembly language statements int x = 123;MOV R1,123 a = b + 34;ADD R3, R4, 34

Register Direct Addressing The operand is held in a register which is specified in instruction.

Register (direct) Addressing Example MOV R3, R2 ;R3 = R2

Register direct addressing used in compiled code Useful for integer variables. For example: High level code Assembly language statements x = y;MOV R1,R2 a = b + c;ADD R3, R4, R5

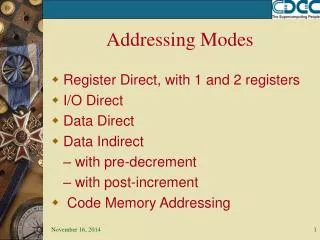

Register Indirect Addressing The operand is held in memory. The address of the operand location is held in a register which is specified in instruction. Useful for accessing different memory locations such as list of consecutive locations. Contents of register can be incremented after each access to point to the next location.

Register Indirect Addressing Example LD R3,[R2] ;R3=contents of memory, address in R2 [ ] read as contents of memory In this example, R2 holds the number 120 For clarity here and later, omitted that memory transfer has 32 bits (4 consecutive bytes) if 32 bit registers.

Example of Register indirect addressing used in compiled code In C, for pointers. High level code Assembly language statements int*b; // ptr, a pointer int a; // a, integer say in memory loc. 120 b = &a; // b = address of a MOV R1,120 *b = 123; // location pointed by b = 123 LD [R1],123

Register Indirect Addressing plus Offset Similar to register indirect addressing except an offset held in the instruction is added to register contents to form the effective address:

Register Indirect Addressing Plus Offset Example LD R3,100[R2] ;R3=contents of memory, address ;in R2 + 100 In this example R2 holds the number 120

Register Indirect Addressing Variation Index Register Addressing Register indirect addressing where register seen as an “index” into a list (one dimensional array). Register holds number of locations from starting point (first item in list). Starting point given in instruction.

Index Register Addressing Example Here, compiler uses R1 for x, R2 for i and starting address for array a is location 100. a[] assumed character array in figure. If a[] is an integer array, would use LD and need to multiply index by 4.

Implied Addressing Some operations have an implicit location for the operand and its address need not be specified. We will come across such operations later.

Specifying addressing mode in machine instruction • Can be specified: • Within operation field (or is implied in operation) or • In a separate mode field

Addressing Mode Specified in Separate Field Actual encoding can be more complex that this.

Size of Transfer Specified in Separate Field Again, this detail is not shown in the following. Actual encoding can be much more complex that this (e.g. Intel processors highly complex).