Project Submission

Project Submission. How to work with MOSIS. Unsponsored usage – PO based MOSIS customer agreement IBM processes – IBM CDA, DKLA Artisan libraries – Artisan agreement Sponsored usage – MEP Instructional accounts – class list Research accounts - proposal Individual NDA, disclosure list

Project Submission

E N D

Presentation Transcript

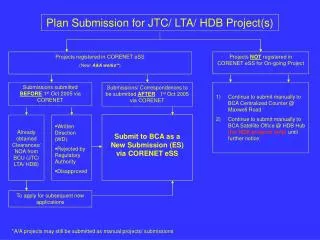

How to work with MOSIS • Unsponsored usage – PO based • MOSIS customer agreement • IBM processes – IBM CDA, DKLA • Artisan libraries – Artisan agreement • Sponsored usage – MEP • Instructional accounts – class list • Research accounts - proposal • Individual NDA, disclosure list • Accounts are per professor

IP protection • IP protection is critical to access to fabrication for universities • Each professor is directly responsible for maintaining the confidentiality of proprietary information obtained from MOSIS • The professor will be held accountable for any disclosure violation by anyone involved with the project (associated faculty or staff, and students) • Each professor responsible for a MOSIS account will control access to MOSIS vendors’ documents • NO PERSON working with the professor may be granted access without first signing the "Statement Acknowledging Responsibility To Protect Proprietary Material" – Professor to maintain disclosure list

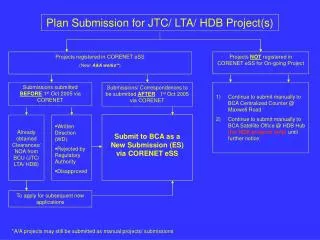

Issues to be aware of • PO based submissions • CMP issues are critical, especially for IBM processes • Run schedule is very tight • Delays for late projects are next to impossible • MEP submissions • In addition to the above • Proposals are needed at least 3 weeks in advance • Artisan instantiation needed 1 week in advance • Proposal acceptance does not guarantee space on a run – designs included on space available basis • IBM processes have more space

Standard Data Preparation • Project Check • Checks design syntax • Checks layer names • Computes the size, counts the pads • Checks actual values with declared values • DRC available (optional) • Data Prep • Sizing, logical operations (inc. OPC)

General Questions • IMPORTANT: Get the GDS file into the system properly, not as an attachment to an e-mail (please: NEVER do this) • MOSIS does not require a seal on the edge of your design • MOSIS will install a seal ring which is part of the definition of the scribe lines for the reticle • This ring will not necessarily be in close proximity to your layout, • If you want a "guardring“ for whatever reasons (of your own), then you should draw it yourself

Compatible Design Libraries • Artisan • Commercial Firms • Free Digital Libraries, I/Os & Memories • TSMC 0.25µ, 0.18µ; IBM 0.18µ, 0.13µ processes • Supports Commercial EDA tools: Cadence, Mentor, Synopsys/Avant! • Universities • Complete front end views of core & I/O cells • Behavioral, synthesis, simulation, P&R • No access to GDS, MOSIS Instantiates the cells

Artisan Instantiation • Library information needed for std cells, IOs, memory instances to generate complete GDS • Example details – user to provide • TSMC C025G (0.25um Baseline) SAGE Standard Cell Library, library "sc" Version "2000q2v0“ • TSMC Linear I/O Library, library "tpz873nez" version "230b" • TSMC 025 High-Density Single-Port SRAM Generator (6T 10.95um^2 Cell), generator "SRAM-SP-HD" version "2002q1v2“ • Also provide memory generator ‘.spec’ file generated by front-end compiler

Design Rule Checking • The design rules which must be followed are posted in the form of DRC decks and Design Rule documents (MOSIS secure doc. server) • MOSIS cannot possibly tell you that violating those rules is safe • MOSIS routinely uses DRACULA for TSMC 0.25, BUT moving to Mentor Graphics' "Calibre" for more advanced technologies • DRACULA works well enough for DRC and antenna checking • For checking connectivity, MOSIS prefers the Calibre LVS deck, • Since the DRACULA decks do not handle MiM metals correctly, this is critical when checking for shorts • Be sure and select the proper variants of the DRC decks; • For example, if you are using thick-top-metal, there is a special set of thick-top-metal decks • If you are using mixed-mode features such as MiM, or strange threshold devices etc., use the mixed-mode decks etc. • Important, no two tools ever give the same flags for the same layout

Design Flows - Digital • Digital flow • Synthesis to place and route • Standard cells and memory generators • IP elements • Artisan std cells, IOs, memories • Virage Logic memory generators • CAD tools • Cadence place and route • Mentor verification • Synopsys synthesis

Design Flows – Mixed Signal • Mixed-signal flow • Schematic capture, simulation • Link to digital flow • CAD tools, design kits • Agilent ADS models (link to Cadence) • Cadence - PDK (Process Design Kit) • Paragon – FDK (Foundry Design Kit) • Tanner – TDB (Tanner DataBase)

Design Flows – Full Custom • Full custom flow • Layout design rules, process parameters, SPICE models • CAD tools, design kits • Cadence – e.g. NCSU design kit • Mentor – e.g. ASIC design kit • Other – IC Editors, Laytools, LASI, Electric, Magic • IP – SCMOS std cells, pads

IBM 0.13µ • Logic process - 8SFG • Artisan libraries – std cells , pads, memory gen. • Cadence P&R, Mentor verification • 8 metal layers, 2-thick (M1, M2, M3, M4, M5, M6, MQ, LM) – all copper • Mixed-signal process - 8RF (8SFG base) • Cadence Analog Artist design kits • Schematic capture, simulation (w/ Agilent ADS models) • 8 (Cu, Al) metal layers (M1, M2, M3 [3 thin], MG, MQ [2 thick], LY, E1, MA [3 RF]) • Supply voltages are 1.2V core; 2.5V I/O

IBM 0.18µ • Logic process – 7SF • Artisan libraries – std cells , pads, memory gen. • Cadence P&R, Mentor verification • 8 metals, (M1, M2, M3, M4, M5, LM) – all copper • Mixed-signal process – 7RF • Cadence Analog Artist design kits • Schematic capture, simulation (w/ Agilent ADS models) • SiGe process – 7WL • 7RF CMOS base plus SiGe (Ft 60 Ghz, Fmax 70 Ghz) • Supply voltages are 1.8V core; 3.3V I/O

Assembly • Plastic • Large portfolio • BGAs – 144 to 456 • QFN – 8 to 64 • QFP – 44 to 256 • TQFP – 32 to 208 • Ceramic • DIP 28, 40 • PGA 65, 84, 108, 121, 132, 145, 181, 209, 257, 391 • LCC 28, 52, 84 • Flip-chip bumping