Power Partitioning for Multiprocessors

Power Partitioning for Multiprocessors. Kai Ma, Amiri-Kamalabad Mojtaba. Background. Problems: Overall power: electricity bill (date center), battery life (embedded system)

Power Partitioning for Multiprocessors

E N D

Presentation Transcript

Power Partitioning for Multiprocessors Kai Ma, Amiri-Kamalabad Mojtaba

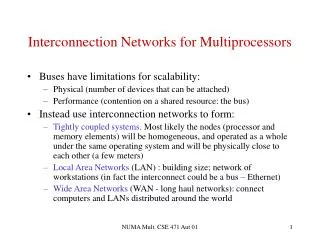

Background • Problems: • Overall power: electricity bill (date center), battery life (embedded system) • On-chip component power: Irregular power characteristics of each components lead to conservative cooling and packaging design. • Power capping or control • Minimizing performance degradation on the condition of capping or controlling power (MICRO06 Isci, HPCA07 Dybdahl, PACT08 Meng)

Motivation • Different applications have different power consumption patterns. • Power consumption in one application could change dramatically . • If adopting pessimistic design, we prepare for peak power dissipation. Most of the time, extra cooling capability will be wasted.

Proposal & Novelties We propose a scheme to control each on-chip component’s power and partition the overall power budget to each component to optimize performance. • Universalize dramatically different components’ characteristics to power consumption and performance contribution trade off, solve the problem in systematic framework (previous: trial-and-error) • Provide upstream and downstream flexibility (previous: case by case)

Design Challenges 1. Power Control for each component 1) Regulate each component’s power behavior 2) Guarantee the whole chip power Challenges: 1) How to guarantee system stability? 2. Power budget partitioning Challenges: 1) How to find the optimal partitioning? 2) How to adapt to different workloads or different execution phase for one workload?

Initial Result • Feedback control can achieve power control goal. • Different power allocations lead to different performance.