Evolving an Adaptive Digital Filter

Evolving an Adaptive Digital Filter. Mohammadreza Baharani University of Tehran School of Electrical and Computer Engineering Spring 2010. Class presentation for the course: “ Custom Implementation of DSP Systems ”

Evolving an Adaptive Digital Filter

E N D

Presentation Transcript

Evolving an Adaptive Digital Filter Mohammadreza Baharani University of TehranSchool of Electrical and Computer Engineering Spring 2010 Class presentation for the course: “Custom Implementation of DSP Systems” All the materials are copy rights of their respective authors as listed in references.

What is evolvable hardware? • Living organisms are complex systems exhibiting a range of desirable characteristics, such as evolution, adaptation, and fault tolerance, which have proved difficult to realize using traditional engineering methodologies. • If one considers life on Earth from its very beginning, the following three levels of organization can be distinguished: [3]

Evolvable Hardware - Continue • Phylogeny: The first level is the temporal evolution of the genetic program, the hallmark of which is the evolution of species, or phylogeny. • Ontogeny: This level constitutes the developmental process of multi cellular organisms. The successive divisions of the mother cell, the zygote, into newly formed cells. • Epigenesis: The ontogenetic program is limited in the amount of information it can store, rendering the complete specification of the organism impossible. [3]

POE Model • Analogous to nature, the space of bio-inspired hardware systems can be partitioned along the phylogenic, ontogenic, and epigenetic axes; we refer to this as the POE model. [3]

GA - Continue [3] [4]

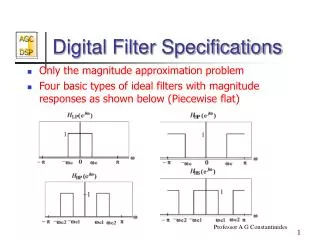

Motivation • One important feature of signal processing is coping with noise. • if the noise level is sufficient or the input signal is not of the required type for the output signal required, then a satisfactory output signal may not be achievable. • To be able to achieve the required output signal for a wide range of input signals and noise, it is desirable to be able to adjust both the characteristics and the type of the filter. • Adaptive filters may be designed to adjust to their environment such that the filter may adapt to noise so as to produce the desired result. [1]

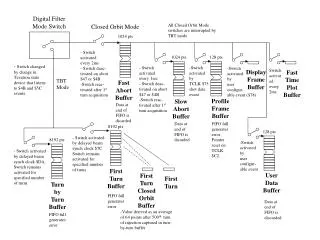

Motivation - continue • Since a DSP processes instructions sequentially, processing of the filter taps is sequential. An FPGA implementation, on the other hand, provides the opportunity to perform the operations required for the filter taps in parallel by implementing multiple filter taps. [1]

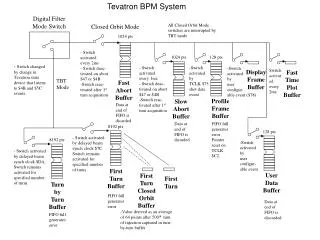

Implementation [1]

Result [1]

Some notes must be considered • Many of today’s digital signal-processing tasks are performed on real-time data. • Areas for real-time adaptive filter utilization can be systems of noise-canceling, filter that automatically adapt to changing environment, and identification of unknown systems where the unknown system can be modeled as a digital filter. • [Knut Arne Vinger et al.] proposed an architecture where can switch in just one clock cycle. [5]

Refrences • [1] G. Tufte and P. Haddow, ‘‘Evolving an Adaptive Digital Filter’’ EH'00, pp 143-150. • [2]: Jason D. Lohn, Gregory S. Hornby. “Evolvable Hardware: Using Evolutionary Computation to Design and Optimize Hardware Systems. • [3] scotthauck and andr´edehon, “reconfigurable computing: the theory and practice of fpga-based computation”. Book Chapter 33-pp725. • [4] Pauline Haddow, Gunnar Tufte and Piet van Remortel, "evolvable hardware: pumping life into dead silicon". • [5] Knut Arne Vinger, Jim Torresen. “Implementing Evolution of FIR-Filters Efficiently in an FPGA”, IEEE Publication, 2003