Midsize Microcontrollers and Microprocessors

Midsize Microcontrollers and Microprocessors. The 8051 is an example of a small inexpensive microcontroller intended for simple applications. Other examples are the PIC and the Atmel AVR. There are also a large number of more powerful “midsize” microcontrollers available.

Midsize Microcontrollers and Microprocessors

E N D

Presentation Transcript

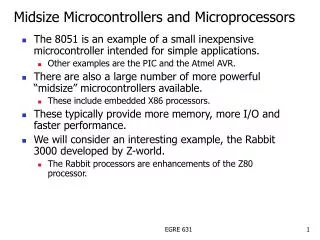

Midsize Microcontrollers and Microprocessors • The 8051 is an example of a small inexpensive microcontroller intended for simple applications. • Other examples are the PIC and the Atmel AVR. • There are also a large number of more powerful “midsize” microcontrollers available. • These include embedded X86 processors. • These typically provide more memory, more I/O and faster performance. • We will consider an interesting example, the Rabbit 3000 developed by Z-world. • The Rabbit processors are enhancements of the Z80 processor. EGRE 631

The 3200 Core module • Rabbit Semiconductor sells the 3000 as a module. • For modest volume applications using this module is more viable than building a system form scratch. EGRE 631

Rabbit 3000 Processor • 8-bit data bus • 20-bit address bus • Internal peripherals use 8 bit address bus • Static design - DC to 54 MHz Clock • Programmable chip select outputs • Clock Spreader results in Ultra-Low EMI • Communication FeaturesHardware and/or software support for TCP/IP, IrDA, SDLC/HDLC, Async, SPI, I2C • 56+ Digital I/O • 6 Serial Ports • 1.8-3.6 V (5 V tolerant I/O) • Watchdog Timer • Extended Low-Power "Sleepy" ModesDynamic, software-enabled low-power modes EGRE 631

Processor Registers • Multiple Accumulators • A – 8 Bit • HL – 16 Bit • Memory Mapping • IX,IY – Index Registers • XPC – Extension of PC • Two Register Banks • A, F, HL, DE, BC all have alternate registers. • EX AF, AF’ swaps AF and A’F’ • EXX swaps HL, DE, and BC with H’L’, D’E’, and B’C’. EGRE 631

Parallel I/O ports • Seven 8-bit I/O ports. (A-F) • I/O pins are shared with other on-chip peripherals. EGRE 631

Other ports • Six Serial Ports • Maximum baud rate of system clock divided by 8 • Several enhancements over standard asynchronous communications. • The serial ports can be used for processor to processor communication. • A parallel slave ports are also provided for processor to processor communication. EGRE 631

Slave port example EGRE 631

Quadrature Decoder • Two channels for encoder input (IQ) • 8-bit counter is incremented or decremented to keep track of encoder’s position. EGRE 631

Pulse width modulation (PWM) channels. • PWM is useful in many applications from audio generation to motor control. • Four independent channels are provided. • The Rabbit PWM module is straightforward—a single 10-bit free-running counter counts from 0x000 to 0x3FF (0 to 1023) and rolls over. The application program loads a PWM “width” register with a value “n.” Out of 1024 counts, the PWM’s output pulse is high for n+1 counts. This gives the application the ability to vary the duty cycle from about 0.1% to 100%. 1024 ticks from timer A9 define the overall period. EGRE 631

Timers – two timer modules A and B EGRE 631

Memory - MMU and MIU • MMU – memory management unit • MIU – memory interface unit • Combination allow for addressing 6 MB • 20-bit physical address for 1 MB • Internally 16 bit address are used (64 KB) • MMU uses special segment registers to map 16 bit address to 20 bit address. EGRE 631

Base (or Root) Segment 0000 00000 • Data Segment X000 DATASEG|000 + X000 • Stack Segment Y000 STACKSEG|000 + Y000 • Extended Memory Segment E000 XPC|000 + E000 EGRE 631

Memory Mapping Example Base (or Root) Segment 0000 00000 Data Segment X000 DATASEG|000 + X000 Stack Segment Y000 STACKSEG|000 + Y000 Extended Memory Segment E000 XPC|000 + E000 Example The MMU registers are set as follows: • XPC = 0x85 • SEGSIZE = 0xD7 • STACKSEG = 0x80 • DATASEG = 0x79 The physical address of the bottom of the xmem segment is given by: 0x85000 + 0x0E000 = 0x93000 The physical address of the bottom of the stack segment is given by: 0x80000 + 0x0D00 = 0x8D000 The physical address of the bottom of the data segment is given by: 0x79000 + 0x07000 = 0x80000 Y X EGRE 631

MIU EGRE 631