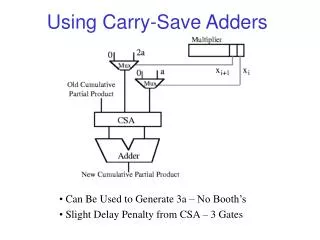

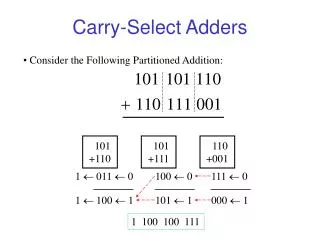

Using Carry-Save Adders

Using Carry-Save Adders. Can Be Used to Generate 3a – No Booth’s Slight Delay Penalty from CSA – 3 Gates. Upper Half P in Stored Carry. Better Use in Keeping Cummulative Product in Redundant Form for First k-1 Cycles Then Use a CPA in the Last Cycle. CSA With Booth Recoding.

Using Carry-Save Adders

E N D

Presentation Transcript

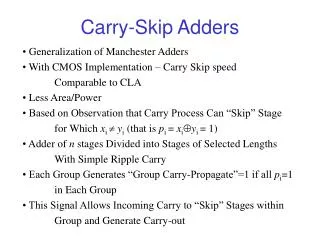

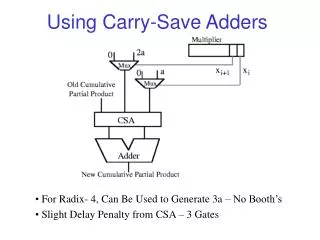

Using Carry-Save Adders • Can Be Used to Generate 3a – No Booth’s • Slight Delay Penalty from CSA – 3 Gates

Upper Half P in Stored Carry • Better Use in Keeping Cummulative Product in Redundant Form for First k-1 Cycles • Then Use a CPA in the Last Cycle

CSA With Booth Recoding • Better Usage when Combined with Booth’s Recoding • Reduces Cycles by 50% • Each Cycle Faster Due to CSA • Sign of a, 2a Incorporated Directly in Recoder/Selector Instead of Add/Subtract Signal Generation

Booth Recoder/Selector • Circuitry Shown on Following Slide • Negative Multiples –a, -2a in 2’s Complement • a, 2a Aligned at Right with Position i • Must be Padded with i Zeros to Right • Bitwise Complement (when –a, -2a Needed) Converts zeros to ones Followed by LSb add of 1 Converts Back to zeros • Causes a Carry-in of 1 into Position i • Can Ignore Positions 0 through i-1 (in neg. multiples) Insert carry-in directly (dot)

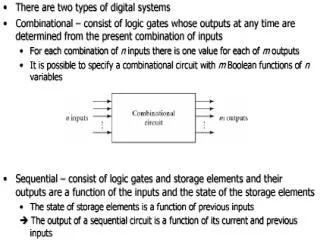

Radices > 4 • Radix-8 (3 bits at a time-k/3 multiples) Requires 3-Level CSA Tree • Might as Well Use Radix-16 (4 bits at a time) • Still 3-level tree with one more CSA • MUXes Can Be Replaced with Booth Recoder/Selector Circuits in Higher Radix Multipliers • Can Continue to Increase Radix (256-8bits) Leading to Wider Trees • Tradeoff is Speed Versus Area