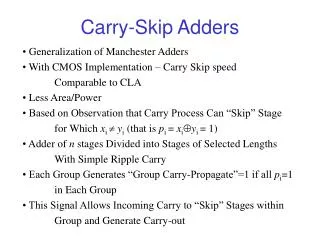

Adders

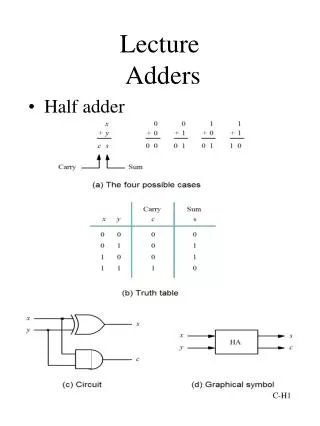

Adders. Adders. Basic Ripple Adders Faster Adders Sequential Adders. The Half Adder. Half Adder Input is limited to 2 bits HS = X xor Y = X•Y’ + X’•Y CO = X•Y Time for the Half Adder? 1 gate delay A gate delay of an xor for the half sum

Adders

E N D

Presentation Transcript

Adders ECE 561 Lecture 15

Adders • Basic Ripple Adders • Faster Adders • Sequential Adders ECE 561 Lecture 15

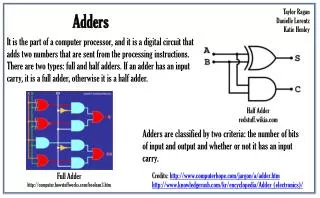

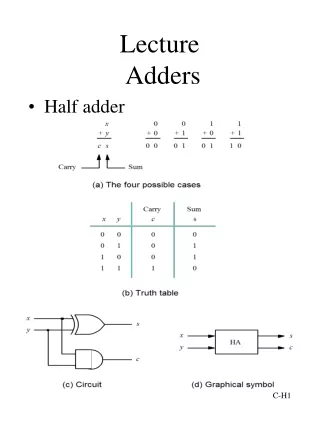

The Half Adder • Half Adder • Input is limited to 2 bits • HS = X xor Y • = X•Y’ + X’•Y • CO = X•Y • Time for the Half Adder? • 1 gate delay • A gate delay of an xor for the half sum • A gate delay of an AND gate for the carry out ECE 561 Lecture 15

The Full Adder • Input is now A B and the Carry in. • So have • S = X xor Y xor Cin • =X•Y’•Cin’+X’•Y•Cin’+X’•Y’•Cin+X•Y•Cin • Cout = X•Y + X•Cin + Y•Cin ECE 561 Lecture 15

The logic • Two level logic • Output delay • A, B Cin Sum • Delay through 2 xor gates • ts = 2 txor • A, B Cin Cout • Delay through an AND gate and an OR gate • tCout = tand + tor ECE 561 Lecture 15

Higher order symbol • When using full adders in a circuit it becomes too cluttered if all gates are shown • Use a symbol for the unit ECE 561 Lecture 15

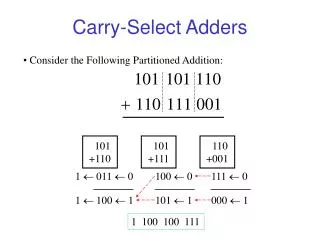

Multiple Bit adders • There are multiple approaches • Most Basic is the Ripple adder • You can also do as good as a ripple adder • One figure of merit to evaluate is the area*time product • In a ripple adder the number of gates (area) grows linearly with the number of bits and the time also grow linearly. ECE 561 Lecture 15

The Ripple Adder • Basic structure • Delay for n bits • tADD = tXYCout + (n-2)tCinCout + tCinS ECE 561 Lecture 15

And in gate delays • tADD = tXYCout + (n-2)tCinCout + tCinS • Where • tXYCout = tand + tor + (n-2) (tand + tor) + txor • = (n-1) (tand + tor) + txor • As number of bits goes up time increases linearlly. Number of gates increases linearly. ECE 561 Lecture 15

Which is more important factor? • Usually time is the more important factor for an add. • Why? • It is on the critical part for the instruction cycle time in any computer. • Why has it become more important today? • Address space has increased, programs are larger more bits in program counter. ECE 561 Lecture 15

How to add faster • The most significant Sum bit of the adder is a function of all the inputs. • Could just do a straight logic equation for each Sum bit as a function of all the bits of which it is a function. • Or use a methodology • That methodology is called carry-lookahead ECE 561 Lecture 15

Carry-Lookahead Adders • Start by defining two functions • Generate gi = xi•yi • Propogate pi = xi + yi • And ci+1 = gi + pi•ci or (expanding out) • Having pi and gi, can now write the carry output of a stage • c1 = g0 + p0 c0 • c2 = g1 + p1 c1 = g1 + p1 (g0 + p0 c0 ) • = g1 + p1 g0 + p1 p0 c0 ECE 561 Lecture 15

CLA continued • c3 = g2 + p2 c2 • = g2 + p2 (g1 + p1 g0 + p1 p0 c0) • = g2 + p2 g1 + p2 p1 g0 + p2 p1 p0 c0 • c4 = g3 + p3 c3 • = g3 + p3 (g2 + p2 g1 + p2 p1 g0 + p2 p1 p0 c0) • = g3+p3g2 + p3p2 g1 + p3p2 p1 g0 + p3p2p1p0c0 • And this can continue for as many bits as you want. ECE 561 Lecture 15

The logic • Implementing into gates ECE 561 Lecture 15

Analysis • Had our time for 4 bit addition from a ripple adder. • Here the slowest bit is the msb output as it has the largest logic function. • Multiple input gates are slower than 2 input gates. • Start with the time for the propagate and generate signal logic • tpg = max(tand , tor ) ECE 561 Lecture 15

Analysis cont • Now must generate s4 output • ts4 = tpg+ tor4+ tand4+ txor • Assume that 4 input gate is ½ the speed of 2 input and gate • Assume xor time is 1.5 the speed of and • ~= 5.5 tand + tpg • If tand ~= tor time is ~= 6.5 tand versus a time of ~2 n tandfor a ripple adder where is the number of bits ECE 561 Lecture 15

In terms of gates • A full adder takes 6 2-input gates • An n-bit ripple adder will take 6n gates • The Carry Lookahead Adder • 1st stage 5 gates (max of 2 input) • 2nd state 7 gates (max of 2 input) • 3rd stage 8 gates (max of 3 input) • 4th stage 9 gates (max of 4 input) • As you use more stage the area grows exponentially if you limit the number of inputs to the gates ECE 561 Lecture 15

Tradeoff • The ripple adder versus the carry look-ahead adder is a classic time and area tradeoff. • In many circuits you can reduce time by using more logic to produce the output more directly. ECE 561 Lecture 15