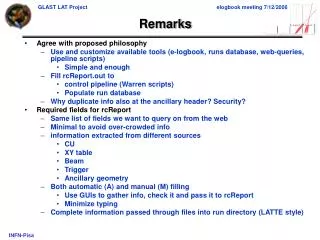

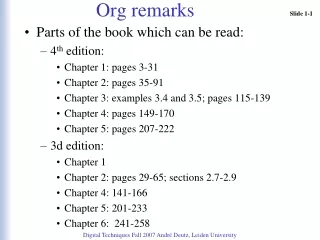

Org remarks

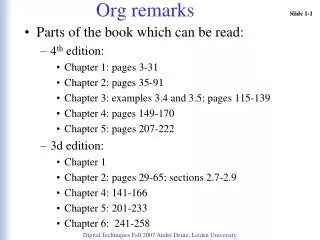

Org remarks. Parts of the book which can be read: 4 th edition: Chapter 1: pages 3-31 Chapter 2: pages 35-91 Chapter 3: examples 3.4 and 3.5; pages 115-139 Chapter 4: pages 149-170 Chapter 5: pages 207-222 3d edition: Chapter 1 Chapter 2: pages 29-65; sections 2.7-2.9

Org remarks

E N D

Presentation Transcript

Org remarks • Parts of the book which can be read: • 4th edition: • Chapter 1: pages 3-31 • Chapter 2: pages 35-91 • Chapter 3: examples 3.4 and 3.5; pages 115-139 • Chapter 4: pages 149-170 • Chapter 5: pages 207-222 • 3d edition: • Chapter 1 • Chapter 2: pages 29-65; sections 2.7-2.9 • Chapter 4: 141-166 • Chapter 5: 201-233 • Chapter 6: 241-258 Digital Techniques Fall 2007 André Deutz, Leiden University

Onto Our Simple One-cycle Instruction Processor • CLUs: Continuation of ALU discussion • CLUs: discussion of algorithms and hardware for multiplication (and discuss the idea of Booth’s algorithm) • Sequential Circuits: Ways of clocking flip-flops • Von Neumann Computer Model • Implementation of the fetch-part of the eternal von Neumann cycle Digital Techniques Fall 2007 André Deutz, Leiden University

An old acquaintance: processor-project assignment 1 (1.3) a b c_in k_1 k_0 2 0 1 r(esult) 1-bit ALU as specified in 1.3 2 + 3 c_out Digital Techniques Fall 2007 André Deutz, Leiden University

An old acquaintance: processor-project assignment 1 (1.3): 1-bit ALU a b c_in k_1 k_0 2 Let us find another implementation Of the 1-bit ALU by constructing The Truth table for r(esult) and c_out Subsequently read off the canonical Sum of minterms for r and c_out, simplify this sum With the Quine-McCluskey Algorithm. Convert the minimized sums into LDs. 0 1 r(esult) 2 + 3 c_out Digital Techniques Fall 2007 André Deutz, Leiden University

1-bit ALU specified in 1.3TT for r and c_out Digital Techniques Fall 2007 André Deutz, Leiden University

Canonical sum for r(esult) and c_out We continue with r: Digital Techniques Fall 2007 André Deutz, Leiden University

Simplification of the expression for r by Quine-McCluskey Digital Techniques Fall 2007 André Deutz, Leiden University

Simplification of the expression for r by Quine-McCluskey Digital Techniques Fall 2007 André Deutz, Leiden University

Simplification of the expression for r by Quine-McCluskey Digital Techniques Fall 2007 André Deutz, Leiden University

Simplification of the expression for r by Quine-McCluskey Digital Techniques Fall 2007 André Deutz, Leiden University

Simplification of the expressionfor r by Quine-McCluskey Digital Techniques Fall 2007 André Deutz, Leiden University

Simplification of the expressionfor r by Quine-McCluskey The red one are the essential prime implicants Digital Techniques Fall 2007 André Deutz, Leiden University

Simplification of the expression for r by Quine-McCluskey Digital Techniques Fall 2007 André Deutz, Leiden University

Simplification of the expressionfor r by Quine-McCluskey Digital Techniques Fall 2007 André Deutz, Leiden University

Construction of LD for r: Digital Techniques Fall 2007 André Deutz, Leiden University

A more realistic ALU Digital Techniques Fall 2007 André Deutz, Leiden University

A more realistic ALU: the MSB slice Digital Techniques Fall 2007 André Deutz, Leiden University

A more realistic ALU carryOut Digital Techniques Fall 2007 André Deutz, Leiden University

Answer to the question of Lecture #1: Bits have no inherent meaning: operations determine whether they are really ASCII characters, integers, floating point numbers … The previous slide (the ALU) makes this point quite tangible! The choice of operation will determine whether the bitstrings a_3a_2a_1a_0 , b_3b_2b_1b_0 and the output bitstring result_3result_2result_1result_0 are viewed as two’s complement (numbers -8 through +7, for a 4-bit ALU) or as binary (numbers 0 through +15). Digital Techniques Fall 2007 André Deutz, Leiden University

Multiplication: towards Booth’s Algorithm Digital Techniques Fall 2007 André Deutz, Leiden University

Multiplication: first attempt 32 bits Shift left 64 bits 64 64 64 bits Digital Techniques Fall 2007 André Deutz, Leiden University

Multiplication: second attempt Hardware: Digital Techniques Fall 2007 André Deutz, Leiden University

Multiplication: second attempt Digital Techniques Fall 2007 André Deutz, Leiden University

Multiplication: third attempt Digital Techniques Fall 2007 André Deutz, Leiden University

Multiplication: third attempt Digital Techniques Fall 2007 André Deutz, Leiden University

Multiplication: Booth’s algorithm • What about signed multiplication? • easiest solution is to make both positive & remember whether to complement product when done (leave out the sign bit, run for 31 steps) • Booth’s Algorithm is more elegant way to multiply signed numbers using same hardware as before Digital Techniques Fall 2007 André Deutz, Leiden University

Motivation for Booth’s algorithm Digital Techniques Fall 2007 André Deutz, Leiden University

Booth’s Algorithm Insight Current Bit Bit to the Right Explanation Example 1 0 Beginning of a run of 1s 0001111000 1 1 Middle of a run of 1s 0001111000 0 1 End of a run of 1s 0001111000 0 0 Middle of a run of 0s 0001111000 Originally for Speed since shift faster than add for his machine

Booth’s Algorithm 1. Depending on the current and previous bits, do one of the following:00: a. Middle of a string of 0s, so no arithmetic operations.01: b. End of a string of 1s, so add the multiplicand to the left half of the product.10: c. Beginning of a string of 1s, so subtract the multiplicand from the left half of the product.11: d. Middle of a string of 1s, so no arithmetic operation. 2. As in the previous algorithm, shift the Product register right (arith) 1 bit. Multiplicand Product (2 x 3)0010 0000 0011 0 Multiplicand Product (2 x -3)0010 0000 1101 0

Sequential circuits • Ways of triggering flip-flops • Whenever the clock is asserted (level sensitive) • Whenever the clock changes state (edge-sensitive) • Capture data on one edge of the clock and transfer it to the output of the following edge(i.e, master-slave flip-flop) Digital Techniques Fall 2007 André Deutz, Leiden University

The von Neumann Model of a computer Digital Techniques Fall 2007 André Deutz, Leiden University

A typical “desktop” system: Digital Techniques Fall 2007 André Deutz, Leiden University

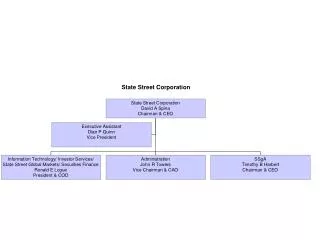

Where is the processor? Digital Techniques Fall 2007 André Deutz, Leiden University

A look at the motherboard: Digital Techniques Fall 2007 André Deutz, Leiden University

Basic functional blocks of a simple computer Digital Techniques Fall 2007 André Deutz, Leiden University Digital Techniques Fall 2007 André Deutz, Leiden University

Basic functional blocks of a simple computer • The CPU, or processor, consists of a datapath and control • The datapath performs arithmetic and logical operations on data stored temporarily in internal registers • The control unit determines exactly what operations are performed. It also controls acccess to memory and I/O devices Digital Techniques Fall 2007 André Deutz, Leiden University

Salient feature of the von Neumann Architecture Storage/memory structure holds both a list of instructions (= program) and data The list of instructions and the data are changeable, making the computer into a universal machine (as opposed to calculators). Digital Techniques Fall 2007 André Deutz, Leiden University

Instruction Processing (von Neumann Cycle -- eternal) Fetch instruction from memory (Increment program counter ) Execute instruction How do you stop this? 4-40 Digital Techniques Fall 2007 André Deutz, Leiden University

Instruction Processing in more detail Fetch instruction from memory (Increment program counter) Decode instruction Evaluate address Fetch operands from memory Execute operation Store result 4-41 Digital Techniques Fall 2007 André Deutz, Leiden University

Von Neumann model • Discussion of model • Eternal von Neumann cycle • Show-and-tell: Digital Works implementation of fetch part of the eternal von Neumann cycle Digital Techniques Fall 2007 André Deutz, Leiden University

Some Details for building our computer Digital Techniques Fall 2007 André Deutz, Leiden University

Single cycle data paths: Assumptions All state elements act like positive edge-triggered flip flops. D Q clk Processor uses synchronous logic design (a “clock”). Reset ? Digital Techniques Fall 2007 André Deutz, Leiden University

A portion of the datapath used for Fetching instructions and incrementing The program counter (PC) Instr Mem Addr Data + 0x1 PC D Q

How data flows after posedge op RegFile Instr Mem 5 rs1 32 32 5 rd1 rs2 5 Addr Data ws 32 32 ALU + Logic rd2 wd 0x1 WE 32 32 PC D Q Digital Techniques Fall 2007 André Deutz, Leiden University

registerfile Chooses first register 4-bit register 4-bit register 4-bit register 4-bit register Data to read from First chosen register Chooses second register Chooses register to be written Data to read from Second chosen register Data to be written Write Enable Digital Techniques Fall 2007 André Deutz, Leiden University Digital Techniques Fall 2007 André Deutz, Leiden University