Metodo di progetto

Metodo di progetto. Descrizione circuito. Specifiche di progetto. Tabella. Risoluzione del problema. Funzione Z=f(X). Sintesi. Sintesi con MUX. Sintesi con NAND/NOR. Sintesi con Gate vari. Numeri pari e dispari.

Metodo di progetto

E N D

Presentation Transcript

Metodo di progetto Descrizione circuito Specifiche di progetto Tabella Risoluzione del problema Funzione Z=f(X) Sintesi Sintesi con MUX Sintesi con NAND/NOR Sintesi con Gate vari

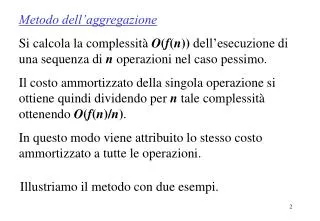

Numeri pari e dispari L’ esercitazione di oggi prevede la progettazione e la simulazione in Quartus II di un circuito che riconosca i numeri pari e dispari. In particolare l’ingresso è a 5 bit X[4..0], dove X[3..0] è una cifra BCD e X4 è un bit per scegliere la modalità di funzionamento del circuito. ? Mode X4 X[3..0] Z B C D Descrizione del circuito:

Numeri pari e dispari X4=0 X4=1

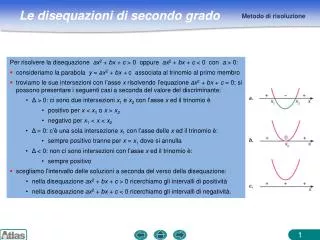

Numeri pari e dispari Ricavare la funzione Z = f(X) = f(X4,X3,X2,X1,X0) Sintetizzare la rete logica utilizzando dei MUX Sintetizzare la stessa rete logica utilizzando solo NAND o NOR, quindi dopo aver ricavato l’espressione minima SP o PS.

Parity bit Ora proviamo a modificare il circuito in modo che invece di rilevare un numero pari/dispari, la rete rilevi un numero pari/dispari di uni (o zeri). Gli ingressi sono sempre gli stessi: X[3..0] è una cifra BCD e X4 seleziona la logica di uscita (logica positiva o logica negativa). ? Mode X4 X[3..0] Z B C D Descrizione del circuito:

Parity bit Linea di trasmissione seriale o parallela, con filo o senza filo D[7..0] Drx[7..0]P(D) D[7..0]P(D) TX RX Drx[7..0] Parity Bit P(D[7..0]) Parity Bit Generator Parity Bit Detector P(Drx)

Parity bit X4=0