FC Video Controller

Technion - Israel institute of technology, department of Electrical Engineering High speed digital systems laboratory. FC Video Controller. Performed by: Kapshitz Tsachy Grinkrug Michael Instructor: Alex Gurevich Cooperated with: Elbit Systems Ltd. Input:

FC Video Controller

E N D

Presentation Transcript

Technion - Israel institute of technology, department of Electrical Engineering High speed digital systems laboratory FC Video Controller Performed by: Kapshitz Tsachy Grinkrug Michael Instructor: Alex Gurevich Cooperated with: Elbit Systems Ltd.

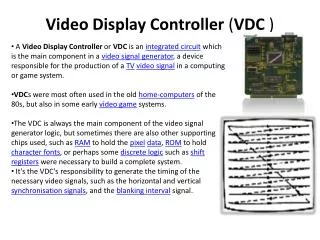

Input: Fiber Channel Frames that include Audio-Visual containers Controller Configuration Output: Video objects in resolution of pixels (pixel per clock) Ancillary objects in resolution of DWords (except the last one) Status Abstract

Input Unit • Combines input words into Dwords • comma signal is passed together with the comma DWord • Generates clk_low clock:clk_low = rclk/2

Frame Controller • Parses Frame Headers • Passes through only legal frames: • SOF • DID • RCTL • TYPE • SEQ • EOF • CRC is calculated by an external unit and the result is compared

Container Controller • Parses Container Header • Type • Index • Size • Extracts ancillary and video objects • Outputs the data through separate interfaces

FS - video Frame Size (in pixels) F1 - Fibre Channel frequency F2 - Aligner frequency (in pixels) SZ1 - FIFO size in case of 1 byte per pixel resolution SZ3 - FIFO size in case of 3 byte per pixel resolution SZ - FIFO size in general case = MAX(SZ1, SZ3) SZ1 = SZ3 = The typical video frame rate is 30 fps => overall byte throughput is: 30xFS 14.5 MHz Thus, synthesizing for clk_high higher than this value and choosing a sufficient FIFO size, the Controller will manage to process the protocol. FIFO size calculation

Let's take some typical values: FS = 910 x 525 = 477750 480KB F1 = 53 MHz F2 = 25 MHz SZ = MAX(365074, 419159) = 419159 ~ 420KB For Apex20KE-1X: FS = 480KB F1 = 53 MHz F2 = 41 MHz SZ ~ 290KB Example

In order to implement the above using the conventional FPGA’s, external FIFO can be used 5 parallel 9x128KB 2 pipelined 80x64KB Manufactures: Cypress IDT ‘Real life’ solution FC - above FIFO External FIFO FC - below FIFO

Testing Process 0 3 3 3 2 1 4 4

SW • AV containers are generated using a SW program, randomizing size and other parameters • The containers are divided into FC frames, randomizing their size and adding frame headers • Expected output files are generated for ancillary and video data separately • This methodology enabled sufficient test case coverage