USBpix Upgrade

ATLAB Annual Assembly 18 th February 2013. USBpix Upgrade. V. Filimonov , T. Hemperek , F. Hügging , H . Krüger , N. Wermes. Outline. Research project overview Migrating from FX2 to FX3 Firmware development. Research project overview. Pixel detector electronics for ATLAS Upgrade

USBpix Upgrade

E N D

Presentation Transcript

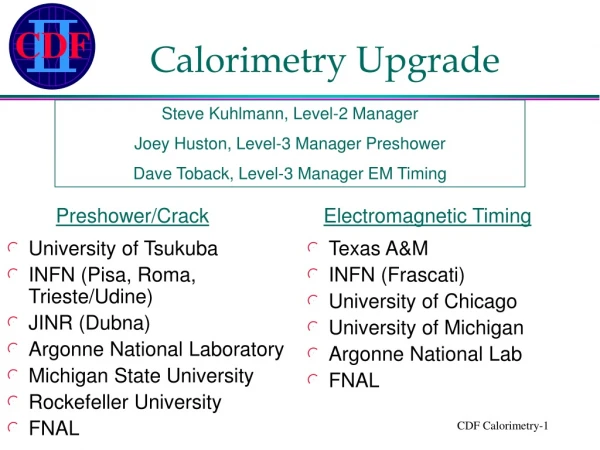

ATLAB Annual Assembly18th February 2013 USBpix Upgrade V. Filimonov, T. Hemperek, F. Hügging,H. Krüger, N. Wermes

Outline • Research project overview • Migrating from FX2 to FX3 • Firmware development USBpix Upgrade

Research project overview • Pixel detector electronics for ATLAS Upgrade • Readout ASICs (FE-I4) • Test environment (USBpix) • HL-LHC outer layers stave concept: • - 1.2 m long stave • - 32 4-chip-modules per stave • 16 on the top, 16 on the bottom USBpix Upgrade

Research project overview • USBpix Test System (Test system hardware) USBpix system for FE-I4 single chip read-out USBpix Upgrade

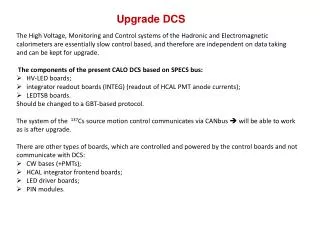

Research project overview • Upgrade Plans for USBpix • Resources on the MultiIO board are coming to their limits • 2 MB SRAM • FPGA resources (Spartan 3, XC3S1000) • Data bandwidth (USB 2.0, ~15 Mbyte/s) • → Simultaneous r/o of four chips and support of new chip generations with higher data rates becomes challenging • Requirements: • – Downward compatible to USBpix adapter cards and SW • KEL connector • USB interface for low-level software compatibility • – larger FPGA and memory • – USB 2.0 →USB 3.0 – Possible data bandwidth (~ 150 Mbyte/s) USBpix Upgrade

Research project overview • Commercial board (Linera FMU3-S6 Series FPGA Module) • Custom made carrier PCB • Upgrade Plans for USBpix • 65mm x 50mm board size • USB3 Connectivity, including software drivers and APIs • Xilinx Spartan6 LX45 application FPGA (Available also with LX150) • 1Gbit DDR3 SDRAM (Optional 2 or 4 Gbit) • MicroSDcard slot, accessible from FPGA • Very easy to integrate: Single 5V supply • Programmable via USB3.0 port, JTAG or the on-board flash • 2 100-pin high speed board-to-board connectors to mount on a host-board • 150 user I/O signals. 72 differential pairs • 8 User LEDs on-board • Pin-compatible with FM-S651 series • On-board, programmable clock generator with 4 output clocks, with available SSC FMU3-S6 series FPGA module USBpix Upgrade

Research project overview • FX3 Firmware • FX3 DVK Board • USB 3.0 interface • Firmware development • FX3 device should be compatible with the software for the 8051 based USB 2.0 microcontroller FX3 device USBpix Upgrade

Migrating from FX2 to FX3 • Architectural Differences USBpix Upgrade

Firmware development FX3 DVK Board Block Diagram USBpix Upgrade

Firmware development • USB 3.0 Interface • 4 endpoints for different transfer types were configured • USB enumeration descriptors were configured • DMA Manual channels were created between USB endpoints and CPU sockets • FX3 is correctly recognized as SiUSB device on Windows 32 and 64-bit USB Device Manager interface USBpix Upgrade

Firmware development • Low performance peripherals (LPP) • I2C EEPROM • Configuration of the interface parameters (100 KHz bit rate, register transfer mode, no bus timeout, no DMA timeout) • I2C transfer (preamble: the slave address, the direction of the transfer, the address inside the slave; wait for ACK) • SPI SPI Flash • Configuration of the interface parameters (8 MHz SPI clock, 8 bits word length, MSB first data shift mode, idles high clock polarity (CPOL = 1), clock phase (slave samples at active-idle edge (CPHA = 1)), active low polarity of SSN line, slave select using FW) • SPI transfer (location: command, page address; set SSN line, erase sector, wait for status) USBpix Upgrade

Firmware development • FX3 – FPGA connectivity GPIF II (General Programmable Interface) • Functions as master or slave • Provides 256 firmware programmable states • Supports 8 bit, 16 bit, and 32 bit parallel data bus • Enables interface frequencies up to 100 MHz • Supports 14 configurable control pins when 32 bit data bus is used. All control pins can be either input/output or bidirectional • Supports 16 configurable control pins when 16 or 8 data bus is used. All control pins can be either input/output or bidirectional USBpix Upgrade

Firmware development • GPIF II Designer • Define the interface in the form of a state machine diagram • The electrical interfacing details should be defined using the Interface definition tab before entering the state machine using the state machine canvas tab USBpix Upgrade

Firmware development • GPIF II Designer USBpix Upgrade

Firmware development • GPIF II Designer USBpix Upgrade

Firmware development IDLE SOF WR_DATA EOF IDLE USBpix Upgrade

Firmware development • GPIF II Designer FMU3-S6 series FPGA module GigaBee Header Baseboard with TE0600 module and cables to connect to FX3 USBpix Upgrade

Firmware development • FX3 device: • Can be programmed with software for the FX3 development kit (USB 3.0) • FPGA: • Can be programmed with JTAG interface (self-made connector +USB-JTAG Programming Cable) FMU3-S6 connected to the power supply, to the host through USB 3.0 interface and to the USB-JTAG Programming cable through the self-made connector. USBpix Upgrade

Firmware development • Response from the FPGA (Timing) USBpix Upgrade

Firmware development • GPIF II Designer (Timing simulation) USBpix Upgrade

Firmware development • Response from the FPGA to the reading access (FX3 delay) • Response from the FPGA to the writing access (FX3 delay) USBpix Upgrade

Firmware development • Response from the FPGA to the reading access (FX3 + FPGA delay) • Response from the FPGA to the writing access (FX3 + FPGA delay) USBpix Upgrade

Firmware development • ChipScope waveform (Writing to the FPGA) USBpix Upgrade

Conclusion • FX3 Firmware • USB 3.0 • GPIF II • Writing to the FPGA • Reading from the FPGA • 4 endpoints for different transfer types were configured • USB enumeration descriptors were configured • DMA Manual channels were created between USB endpoints and CPU sockets • Correctly recognized as SiUSB device on Windows 32 and 64-bit • I2C EEPROM • SPI SPI Flash USBpix Upgrade

Conclusion • Next steps • FPGA firmware (started) • FX3 firmware (should be modified every time FPGA timing changes) • PCB design of the new MultiIO Board USBpix Upgrade

Contact Information ViacheslavFilimonov filimonov@physik.uni-bonn.de USBpix Upgrade

Backup EZ USB FX3 System Diagram SPI Flash 4 Mbit EEPROM 64kB USBpix Upgrade

Backup EZ USB FX3 System Diagram USBpix Upgrade

Backup (Currently 8 MHz) USBpix Upgrade

Backup USBpix Upgrade

Backup Programming View of FX3 USBpix Upgrade

Backup DMA Mechanism System Memory USBpix Upgrade

Backup DMA Components USBpix Upgrade

Backup USB Comparison USBpix Upgrade

Backup • Changes in USB 3.0 • SuperSpeed— New higher signaling rate of 5Gbps (625MB/sec) • Dual-bus architecture — Low-Speed, Full-Speed, and High-Speed bus plus SuperSpeedbus • Asynchronous instead of polled traffic flow • Dual-simplex simultaneous bi-directional data flow for SuperSpeed instead of half-duplex unidirectional data flow • Support for streaming • Fast Sync-N-Go technology • Support for higher power • Better power management USBpix Upgrade

Backup USB 3.0 Pin Description Electrical Interface USB 3.0’s pinout is different from that of USB 2.0. Besides the VBUS, D-, D+, and GND pins required for 2.0, 3.0 has five additional pins – two differential pairs plus one ground (GND_DRAIN). The two differential pairs are for SuperSpeed data transfer, supporting dual simplex SuperSpeed signaling. The added GND_DRAIN pin is for drain wire termination, managing signal integrity, and EMI performance. For high throughput and biwire transfer, USB 3.0 defines nine pins to enhance this feature. These pins contain four pins for USB 2.0 and five additional pins for 3.0. Table 1 shows the description of these nine pins. USBpix Upgrade