Real-Time Arbitrary Generator with Dynamic Memory Design Overview

This presentation introduces the design and functionality of a Real-Time Arbitrary Generator (RTAG) that utilizes dynamic memory. It covers essential aspects, including the architectural dilemmas encountered during development, scheduling of tasks, functional specifications, and the implementation process over a 14-week timeline. Our goal is to create a basic Arbitrary Generator that generates sample waves such as sine, triangle, and square, uploads them to the RTAG, and produces output through a DAC upon triggering.

Real-Time Arbitrary Generator with Dynamic Memory Design Overview

E N D

Presentation Transcript

basic Real Time Arbitrary Generator with Dynamic Memory • By: Jonathan Cohen • Itamar Friedman • Instructor: Michael Yampolsky • At the High Speed Digital System Lab Real-Time Arbitrary Generator

Real-Time Arbitrary Generator Design Presentation • Presentation main topics: • General (-reminder) • Functional Spec • Design: • Main Architecture Dilemmas • Chosen Architecture • Time Schedule

Real-Time Arbitrary Generator Our System – Reminder: DSP RTAG D/A • We make a sample wave on PC, store it on our board, and on trigger we produce the wave through D/A

Real-Time Arbitrary Generator Reminder: • Our main Goal: • POC – basic Arbitrary Generator based on Dynamic Memory RTAG

Real-Time Arbitrary Generator Functional SPEC: DSP • A C/C++ program: • Creates sample waves • sin, triangle, square • Uploads the wave to the RTAG • triggers the HW

Real-Time Arbitrary Generator Functional SPEC: • 1: • Gets sample waves in • writes Commands: • Number of points • Data (the wave) • Gets the trigger command: • expendable 1 2 RTAG

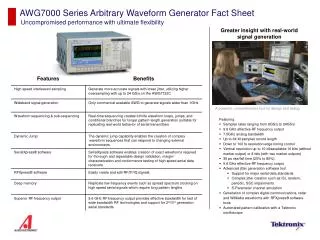

Real-Time Arbitrary Generator Functional SPEC: • 2: Sends Data (to DAC) : • synchronically • cyclic • output streaming frequency rate by request 1 2 RTAG

Real-Time Arbitrary Generator D/A Functional SPEC: • DAC: • Gets 16 bit sample wave • Makes Analog wave – of course

Real-Time Arbitrary Generator Design – Main Dilemmas: • Handle memory refreshing by: • Self refreshing: • Splitting the data over all the memory, and accessing the data frequently. • Memory Controller: • an component that will refresh the memory, and data will be stored regularly.

Real-Time Arbitrary Generator Design – Main Dilemmas: • One or Two clocks ? • One – for entire system • OR • Two – one for the RTAG, and another for the DAC • One wave for all frequency range OR to build a wave for each frequency ?

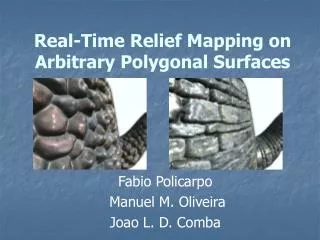

Real-Time Arbitrary Generator Chosen Architecture: PC DAC PC - “DSP” C++ Program Wave Maker Controller Gidel Card FPGA- Altera , Clock=100MHz Reg DAC MC FIFO PLL DDR2

Real-Time Arbitrary Generator • Main Idea: • All waves are generated by the “DSP” unit, then uploaded to DDR2 • The first wave points are uploaded to the FIFO unit • At trigger the Data streams from FIFO unit to the DAC through a Register Chosen Architecture :

Real-Time Arbitrary Generator • Main Idea: • Almost all entities works with local clock at maximum frequency : 100 MHz • But – the Register works with an external clock, changing between 10Hz to 50 MHZ. Chosen Architecture :

Real-Time Arbitrary Generator Controller functionality: • Main Idea: • controls the flow of data • “Talks” with: “DSP”, MC, FIFO, Reg • Routes sample waves from the DSP the MC • Routes the wave points to the FIFO. And controlling the FIFO.

Real-Time Arbitrary Generator MC functionality: • Main Idea: • Controls the Memory (DDR2) • “Talks” with: Controller, DDR2, FIFO • Writes sample waves to DDR2 • Reads sample waves to DDR2 • Controls the DDR2: • refreshing • maintenance

Real-Time Arbitrary Generator FIFO functionality: • Main Idea: • “Gateway” between Memory to • “Talks” with: Controller, DAC • Gets Data at 100 MHz • Pups Data at requested frequency (pll) • Indicates: full, empty, half

Real-Time Arbitrary Generator • Main Idea: • User Interface. Creats commands to HW • “Talks” with: Controller, MC, PLL • makes vectors waves: sin, triangle, square • dsp_make_wave <int Npoints> <string wave> • Sends Waves to Controller • dsp_send_wave <int identifier> • Sends trigger to Controller: • dsp_send_trig DSP functionality :

Real-Time Arbitrary Generator Time Schedule: 0weeks 14weeks • Tasks: • Presentations: • Final: • Thus Far - Final report Part A • Tasks for Second semester • Implementation: • RTAG infrastructure • A basic running system

Real-Time Arbitrary Generator Time Schedule: • Implementation: • 1-6/6 : creating simple units • 7-15/6 : creating MC example • 16/6 : We are Here • 17-20/6 : creating protocols • 20/6-24/7 : Exams period • 25-31/7 : implementing HW • 1-6/8 : implementing SW • 7-10/8: integration 0weeks 14weeks

Real-Time Arbitrary Generator Time Schedule: 0weeks 14weeks • Next Semester: • Implementation • Verification, Testing, Reviewing • Final tuning • presentations & Final report

Real-Time Arbitrary Generator See You Next Time: • Real Time Arbitrary Generator with dynamic memory • Jony & Ita • HS-DSL: Spring 2009