basic Real Time Arbitrary Generator with Dynamic Memory

This presentation explores the innovative design of a Real-Time Arbitrary Generator (RTAG) utilizing dynamic memory (DDR2/DDR3) to overcome the limitations of static memory in traditional generators. Key topics include the motivation behind this development, comprehensive requirements, functional specifications, and an initial design overview. We will also discuss the project's timeline and tasks, focusing on the benefits of faster and cost-effective memory solutions. Join us as we present our progress and findings, paving the way for advanced digital signal generation in high-speed applications.

basic Real Time Arbitrary Generator with Dynamic Memory

E N D

Presentation Transcript

basic Real Time Arbitrary Generator with Dynamic Memory • By: Jonathan Cohen • Itamar Friedman • Instructor: Michael Yampolsky • At the High Speed Digital System Lab Real-Time Arbitrary Generator

Real-Time Arbitrary Generator basic Real Time Arbitrary Generator with Dynamic Memory • Presentation main topics: • The Idea • Requirements • Preliminary Functional Spec • Initial Design (very shortly) • Time Schedule

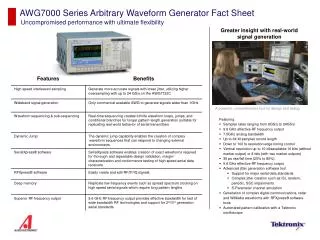

Real-Time Arbitrary Generator The Idea: • The Motivation: • The bottleneck of Arbitrary generator manufacturers is the static memory component. • What makes it a bottleneck: • It’s Slow • It’s Expensive • It’s embedded into the board

Real-Time Arbitrary Generator The Idea: • Our Solution: • Dynamic Memory • such as: DDR2 or DDR3 • fast • cheap • easy to replace

Real-Time Arbitrary Generator The Idea: • Why did not the industry developed Arbitrary generator with dynamic memory until now: • Real-Time problems: • refreshing • memory control • Paradigm: • POC?

Real-Time Arbitrary Generator Requirements: • Our main Goal: • POC – basic Arbitrary Generator based on Dynamic Memory RTAG

Real-Time Arbitrary Generator Requirements: 1 2 DSP RTAG D/A • 1: The RTAG Gets the Data (waves samples) from the DSP • 2: The RTAG streams the Data forward, starting on trigger (cyclic)

Real-Time Arbitrary Generator Requirements: • Read and Write, simultaneously • Sends Data synchronically • Streams the Data forwards: • Beside to a initial delay (one clock from trigger) , streams the Data continuously • Output signals frequency rates: • 10Hz-50 MHz • Input & Output width: 16 bit RTAG

Real-Time Arbitrary Generator Preliminary Functional SPEC: • 1: • Gets sample wave • writes Commands: • Wave Number (identifier) • Number of points • Data (the wave) • Gets trigger commands: • which wave to stream on trigger • the trigger 1 2 RTAG

Real-Time Arbitrary Generator Preliminary Functional SPEC: • 2: Sends Data (to DAC) : • synchronically • cyclic • output streaming frequency rate by request 1 2 RTAG

Real-Time Arbitrary Generator Initial Design: FPGA Controller FIFO MC DDR • RTAG

Real-Time Arbitrary Generator Time Schedule: 0weeks 14weeks • Tasks: • Acquaintance: • GiDEL Tools • Altera Tools • Synthesis Tools • Verilog • DDRs • …

Real-Time Arbitrary Generator Time Schedule: 0weeks 14weeks • Tasks: • Understanding fully the project Requirements & functional Spec • Thinking about the Architecture • Planning detailed time schedule (more specific than it is today) • We are Here Today

Real-Time Arbitrary Generator Time Schedule: 0weeks 14weeks • Tasks: • Design: • FPGA: • controller, Data Path, … • Board: • connections • DAC • etc…

Real-Time Arbitrary Generator Time Schedule: 0weeks 14weeks • Tasks: • Presentations: • Mid: • design • Final: • Thus Far - Final report • Tasks for Second semester

Real-Time Arbitrary Generator Time Schedule: 0weeks 14weeks • Tasks: • Implementation: • RTAG infrastructure • A basic running system

Real-Time Arbitrary Generator Time Schedule: 0weeks 14weeks • Next Semester: • Implementation • Verification, Testing, Reviewing • Final tuning • presentations & Final report

Real-Time Arbitrary Generator See You Next Time: • Real Time Arbitrary Generator with dynamic memory • Jony & Ita • HS-DSL: Spring 2009