Timing Model

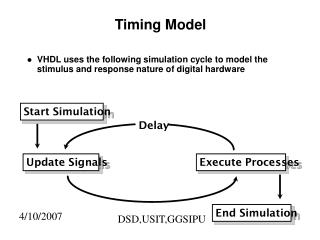

Timing Model. VHDL uses the following simulation cycle to model the stimulus and response nature of digital hardware. Start Simulation. Delay. Update Signals. Execute Processes. End Simulation. Delay Types.

Timing Model

E N D

Presentation Transcript

Timing Model • VHDL uses the following simulation cycle to model the stimulus and response nature of digital hardware Start Simulation Delay Update Signals Execute Processes End Simulation

Delay Types • All VHDL signal assignment statements prescribe an amount of time that must transpire before the signal assumes its new value • This prescribed delay can be in one of three forms: • Transport -- prescribes propagation delay only • Inertial -- prescribes propagation delay and minimum input pulse width • Delta -- the default if no delay time is explicitly specified Input Output delay

Delta Delay • A delta delay is a very small delay (infinitesimally). • It does not correspond to any real delay, and actual simulation time does not advance. • Delta delay allows for ordering of events that occur at the same simulation time during a simulation. • Each unit of simulation time can be considered to be composed of an infinite number of simulation time plus an integral multiple of delta delays.

Delta Delay • Default signal assignment propagation delay if no delay is explicitly prescribed • VHDL signal assignments do not take place immediately • Delta is an infinitesimal VHDL time unit so that all signal assignments can result in signals assuming their values at a future time • E.g. • Supports a model of concurrent VHDL process execution • Order in which processes are executed by simulator does not affect simulation output Output <= NOT Input; -- Output assumes new value in one delta cycle

A IN: 1->0 C B 1 Delta DelayAn Example without Delta Delay • What is the behavior of C? AND gate evaluated first: IN: 1->0 A: 0->1 C: 0->1 B: 1->0 C: 1->0 NAND gate evaluated first: IN: 1->0 A: 0->1 B: 1->0 C: 0->0

Delta DelayAn Example with Delta Delay A • What is the behavior of C? IN: 1->0 C B 1 Using delta delay scheduling TimeDeltaEvent 0 ns 1 IN: 1->0 eval INVERTER 2 A: 0->1 eval NAND, AND 3 B: 1->0 C: 0->1 eval AND 4 C: 1->0 1 ns

Input Output Input Output Transport Delay • Transport delay must be explicitly specified • I.e. keyword “TRANSPORT” must be used • Signal will assume its new value after specified delay -- TRANSPORT delay example Output <= TRANSPORT NOT Input AFTER 10 ns; 0 5 10 15 20 25 30 35

Inertial delay model • An input value must be stable for a specified pulse rejection limit duration before the value is allowed to propagate to the output. • Example: Z <= reject 4ns inertial A after 10 ns; Default delay model.

Input Input Output Output Inertial Delay • Provides for specification propagation delay and input pulse width, i.e. ‘inertia’ of output: • Inertial delay is default and REJECT is optional : target <= [REJECT time_expression] INERTIAL waveform; Output <= NOT Input AFTER 10 ns; -- Propagation delay and minimum pulse width are 10ns 0 5 10 15 20 25 30 35

Inertial Delay (cont.) • Example of gate with ‘inertia’ smaller than propagation delay • e.g. Inverter with propagation delay of 10ns which suppresses pulses shorter than 5ns • Note: the REJECT feature is new to VHDL 1076-1993 Output <= REJECT 5ns INERTIAL NOT Input AFTER 10ns; Input Output 0 5 10 15 20 25 30 35

Signal Waveforms • It is possible to assign multiple values to a signal, each with a different delay value. For example: Phase1 <= ‘0’, ‘1’ after 8ns, ‘0’ after 13 ns, ‘1’ after 50 ns; A more general syntax: Signal object <= [transport | [ reject pulse_rejection_limit] inertial ] waveform-element, waveform-element;

Wait Statement Wait Statement: provides a way to suspend the execution of a process –process always suspends after execution the last statement. –There are three basic forms of the wait statement. –wait on sensitivity list; –wait until boolean-expression; –wait for time-expression; –they may also combined in a single wait statement:–wait on sensitivity-list until boolean-expression for time-expression;

Wait Statement (cont.) Examples:- 1. wait on A, B, C; 2. wait until A= B; 3. wait for10 ns; 4. wait on clock for20 ns; 5. wait until SUM >100 for50 ms; – the process suspends for a maximum of 50 ms until the value of signal SUM is greater than 100. – If the Boolean condition is not satisfied for 50 ms, the process resumes from the statement following the wait statement

6. wait on clock until SUM> 100; –continue to wait if SUM <= 100 the process suspends for a maximum of 50 ms until the value of signal SUM is greater than 100. –If the Boolean condition is not satisfied for 50 ms, the process resumes from the statement following the wait statement

Wait Statement (cont.) – It is possible for a process not to have an explicit sensitivity list – The process may have one or more wait statements • the process must have at least one wait statement; • otherwise, it will never get suspended (infinite loop)

Wait Statement (Example) process --no sensitivity list variable temp1, temp2: BIT; begin temp1 := A and B; temp2 := C and D; temp1 := temp1 or temp2; Z <= not temp1 wait on A, B, C, D; --replaces the sensitivity list end process;

Wait example WAIT0 : process begin wait on DATA; sig_A <= DATA; wait for 0 ns; sig_B <= Sig_A; end process;

Null Statement • Null Statement: is a sequential statement that does not cause any action to take place. - Execution will continues with the next statement – can be used in an if or in case statement The format: null;