Timing

Timing. Outline Block diagram overview of the timing system Where were we at time of last FAC? What has happened since then? How will this work anyway? How does it look from a users point of view? What do we still not know? Tasks remaining: plans/schedule. Timing System.

Timing

E N D

Presentation Transcript

Timing • Outline • Block diagram overview of the timing system • Where were we at time of last FAC? • What has happened since then? • How will this work anyway? • How does it look from a users point of view? • What do we still not know? • Tasks remaining: plans/schedule

Where were we at time of last FAC? • PNET driver done • EVG/EVR 100 series hardware in house • could send events from EVG to EVR but not PNET data • Working with other labs and Micro-Research Finland (MRF) to consolidate our requests for a new version of the hardware

What has happened since then? • Received the EVG/EVR 200 series VME hardware (which sends up to 2K data buffer) • Adapted driver and device support to: • send the PNET data buffer (measured 66 µs transfer) • be OSI (running on mvme6100, RTEMS4.7) • with help from Till Straumann, Eric Bjorklund, Timo Korhonen, Jukka Pietarinen and Bob Dalesio • Wrote Timing Trigger System Engineering Manual • Received the EVR 200 series PMC module • Installed fiber optic network in Bldg 280 for testing

What has happened since then? (2) • Stephanie is setting up a hardware teststand with separate IOCs for EVG and EVR in Bldg 34 for CPE engineers to do: • Timing comparison with existing CAMAC timing system (MPG/PDU) • Timing measurements – jitter, etc • Shakedown by the experts • Test stand to include: • EVG, PNET, EVR, EVR transition module, EVG fanout later • Inputs: PNET pattern from CAMAC timing system, fiducial trigger, and 476Mhz clock • Outputs: EVR front panel and back transition module • Infrastructure: VME crates, dedicated terminal server, dedicated PC, fiber between EVG and EVR • EPICS: test databases and displays, EVR done, EVG in-progress

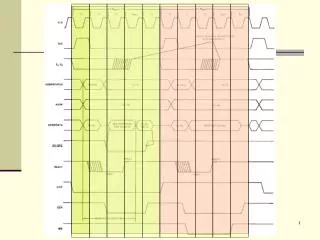

Timescale for event code transfer Event Code 1 Hz event 10 Hz event Beam On Laser event BPM event RF event 360 Hz fiducial 0 . 5 1 . 0 1 . 5 2 . 0 0 . 0 2 . 5 Time after fiducial that event code is sent ( millisec ) LCLS timeslot shown

Timescale for event buffer transfer Time to send 16 byte event buffer from EVG to EVR: 66.4 µs

What do we still not know? • Verify jitter • Verify fiber optic performance (multi vs single mode) • Licensing agreement with MRF

Tasks remaining: plans • Finish PMC-EVR driver • EVG sequence RAM programming at 360 Hz • EVG rules definition • MPS hardware interface • Migrate PNET receiver data records to EVR data records • Full-integration of PMC-EVR with VME-EVR software for easier maintenance • Operator interface – panels to set rate limits, do single shot • Fanout and transition module integration and testing • Installation at sector 20

Tasks remaining: high-level s/w plans • Interface Control Document + review, May • EVG input and output • HW and SW trigger list per subsystem • Applications using the timing pattern • Record (maybe IOC) timestamping • Beam-synchronous acquisition and control • Use writeup provided by Bob Dalesio • Design Document + review, June • Beam-Synchronous Control: rules and algorithm for creating EVG trigger sequences on a pulse-to-pulse basis – algorithm changes based on user requests • Beam-Synchronous Acquisition: mechanism for users to request pulse-by-pulse acquisition (single-shot or buffered) across multiple IOCs based on specified conditions • Proper timing pattern in-place before a fiducial for record processing after fiducial • Implementation of above design plus: • Integration with SLC-aware BPM acquisition • Missing functionality in existing EVG and EVR records for HW upgrade • User-friendly database layer on top of low-level EVR records

Tasks remaining: schedule • We’re in the process of redoing/updating the work breakdown schedule. A draft is due by end of April and final version in May.