Read Timing

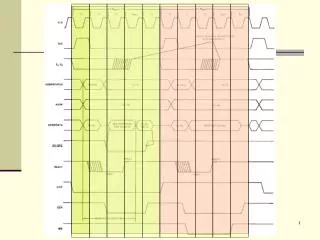

Read Timing. Memory Access Time. Memory Access Time Starts when Address Appears on the Address Bus Ends when Data is sampled by the processor Memory Access Time is approximately 3 T states. Memory Access Time. Address appears after T CLAV (Address Valid Delay) time

Read Timing

E N D

Presentation Transcript

Read Timing Lecture 05

Memory Access Time • Memory Access Time • Starts when Address Appears on the Address Bus • Ends when Data is sampled by the processor • Memory Access Time is approximately 3 T states Lecture 05

Memory Access Time • Address appears after • TCLAV (Address Valid Delay) time • 110 nsec if clock is 5 MHz • Data should be setup at least • TDVCL (Data in Setup Time) time before it is latched by processor • 30 nsec if clock 5 MHz • Memory Access Time = 600 – 110 – 30 = 460 nsec Lecture 05

Memory Write • Data is written at trailing edge of WR*signal • Data has to be held stable for a minimum time period (Data Hold Time) • TWHDX (Data Hold Time after WR*) Data held after WR* signal • 88 nsec if clock 5 MHz • Hold time for Memory is 0 nsec Lecture 05

Ready Signal and the Wait State • READY input causes WAIT states for slower memory and IO • WAIT State is an extra clocking period TW inserted between T2 and T3 • READY synchronization circuitry inside 8284 Clock generator synchronizes the insertion of WAIT States Lecture 05

WAIT States Lecture 05

WAIT States Lecture 05