A Depth-First-Search Controlled Gridless Incremental Routing Algorithm for VLSI Circuits

This paper presents a novel depth-first search (DFS) controlled incremental routing algorithm specifically designed for VLSI circuits. As chip sizes shrink and operational frequencies increase, effective interconnection becomes critical, facing challenges like wire congestion and crosstalk. Our approach focuses on maintaining existing routing as much as possible while accommodating new routing needs through efficient use of space and minimizing perturbations. We demonstrate the effectiveness of our DSR algorithm in experimental results, showing significant improvements over traditional methods in meeting design constraints while ensuring quality routing.

A Depth-First-Search Controlled Gridless Incremental Routing Algorithm for VLSI Circuits

E N D

Presentation Transcript

A Depth-First-Search Controlled Gridless Incremental Routing Algorithm for VLSI Circuits Hasan Arslan and Shantanu Dutt Electrical & Computer Eng. University of Illinois at Chicago ICCD 2004

Outline • Introduction • Importance of Incremental Routing • Previous work • Our Goals • A DFS-Based Incr. Routing Alg. • Non-Uniform Grids • DSR (Depth first search controlled Segment bump and Refit) Algorithm • Experimental Results • Conclusion

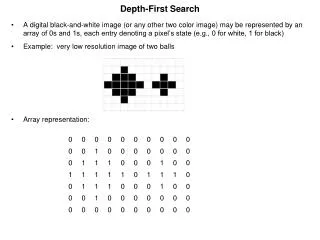

Introduction • In current VLSI Chip • The size gets smaller • High clock frequency • Interconnections on chip very important • Technical Problems • Wire-congestion and routability • Crosstalk / noise • Power consumption • Terminal distribution

Incremental Routing • After a chip layout is completed • Time/noise violation • One or more optimization metrics • Technology constraints • Make changes to the circuit/system • Engineering Change Order (ECO) process • Time to meet market requirements • Enormous resources and time already spent. • Need a time-efficient & effective incremental routing algorithm

Incremental Routing (Cont.) • Incremental Routing Problem • Set of existing routed nets R • Set of new nets S(due to timing violation, noise…) • Quality metrics for an Incr. Routing • Near-optimal incr. solutions in a short amount of time • Preserve previous routing results as much as possible • Complete the required incremental routing in the available channel area if such a solution exists

Prior work on Incremental Routing • 1)Emmert and Bhatia, “Incremental Routing in FPGA” , IEEE Int. ASIC Conference, 1998. • 2)Cong and Sarrafzadeh, “Incremental Physical Design” , ISPD 2000. • 3)Dutt, Shanmugavel and Trimberger, “Efficient Incremental Rerouting for Fault Reconfiguration in FPGAs”, ICCAD 1999. • 4)Dutt, Verma and Arslan “A Search-Based Bump and Refit Approach to Incremental Routing for ECO Applications in FPGAs”, TODAES 2002 • 5)Xiang, Chao, Wong “An ECO Algorithm for Eliminating Crossalk Violations”, ISPD 2004

Emmert-Bhatia (ASIC’98) • Nets connected to faulty PLB, deleted and rerouted • A graph is built, from source pin to target pin • Standard single-net routing mode (global then detailed) • Do not perturb or move existing nets Cong-Sarrafzadeh (ISPD’00) • Single Net Routing : Route new nets without removing any existing nets. • Rip & Reroute : If some nets cannot be routed, rip-up the existing nets which occupy the resources of new nets. Reroute the ripped up nets.

Dutt, Shanmugavel and Trimberger (ICCAD’99) • Used incremental rerouting for dynamic fault reconfiguration in FPGAs • Does not rip-up and reroute • Shift them (or their subnets) to other track positions ---Bump-&-Refit (B&R) • No change in topology, length of existing nets • Optimal: Finds a detailed route if exists Dutt, Verma and Arslan (TODAES’02) • Extended basic B&R significantly for: • full incremental routing (global + detailed) • complex switchboxes • much better results than Std and R&R (routing succ within avail res, HP of failed nets, speed under certain conditions)

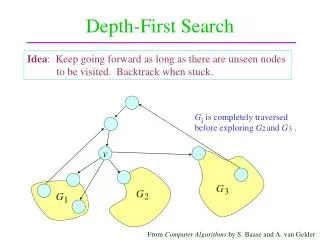

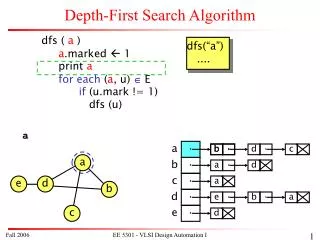

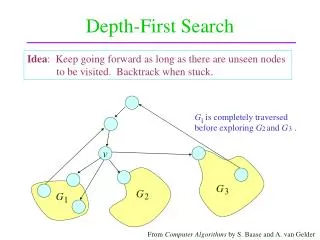

Our Goals • Incremental routing for VLSI (ASIC) circuits • Gridless framework for non-uniform width & spacing req. and memory & time efficiency • Address the quality metrics of incr. routing • Near-optimal incr. solutions (min. WL and vias) in a short amt. of time • Preserve previous routing results as much as possible • Complete the required incremental routing in the available channel area if such a solution exists = min. # of metal layers = max. routing success in given layers • Approach: • Allow bumping of existing nets for near-optimal solns to new nets • However, to obtain an overall good solution control the amount of perturbation of existing nets or their routing failures by retracting their bumpings using an overall DFS control

Adjacent-via R-BBox DFS-Based Incr. Routing Alg.(Incr. Routing Concepts) n1 n 2 n 2 n 1

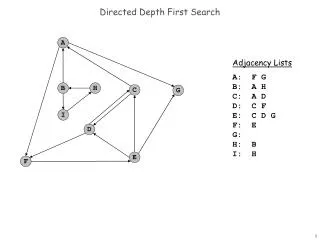

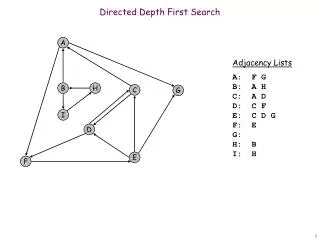

CG of n 1 n v n h n 1. 1 1. 1 1 1 1 ob possible v v 1 ob 2. 1. overlapping 1 n n n h 2. 1 n 2 n v n h 2. 1 n h 2. 1 1. 1 CG of n 2 DFS-Based Incr. Routing Alg.(Incr. Routing Concepts) • If there is an edge between two nets in OG, they might bump each other during shifting one of them. • For net ni in OG • higher degree (more adj. net in OG) might bump more nets, • passing through in dense area • Check only adj. nets/blocks in OG to create non-uniform grid for ni

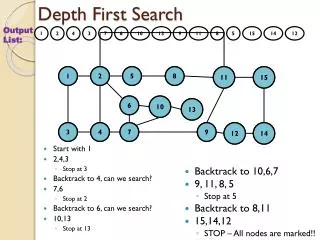

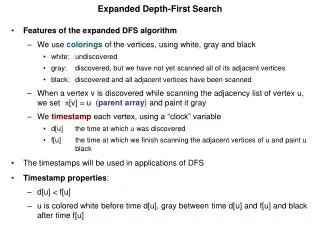

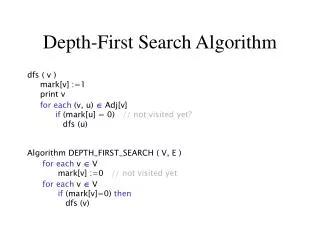

DFS-Based Incr. Routing Alg. Do-DFS-Routing(ni) Route-with-Bumping(ni) Cp=Get-Candidate-Paths Generate grid line in R-BB Route-without-Bumping(ni) All paths in Cp tested? return(fail) YES return(succ.) Soln? For each bumped net nk Do-DFS-Routing(nk) NO Route-with-Bumping(ni) YES return(succ.) Soln? NO YES Soln? Retract curr. bumping-causing routing path NO return(fail)

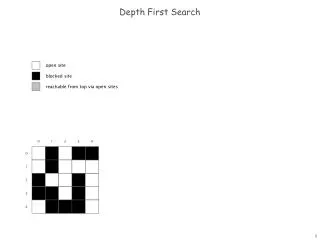

Non-Uniform Grid Extraction • Variable width/spacing rule Width / space req. of new net • To route new net • Create obstruction zone around existing nets • Find zero width path for new net

BGLs (Boundary Grid Lines) OGLs (Occupied Grid Lines) VGLs (Vacant Grid Lines) Non-Uniform Grid Extr. & Routing t s • Use VGLs to get solution without bumping . • Use VGLs and OGLs to do B&R type routing (OGLs has higher cost than VGLs).

DFS-Based Incr. Routing Alg. Do-DFS-Routing(ni) Route-with-Bumping(ni) Cp=Get-Candidate-Paths Generate grid line in R-BB YES Route-without-Bumping(ni) All paths in Cp tested? return(fail) NO YES return(succ.) Soln? Get-Next-Path(CP) For each bumped net nk Do-DFS-Routing(nk) NO Route-with-Bumping(ni) YES return(succ.) Soln? YES Soln? NO Retract curr. bumping-causing Routing path NO return(fail)

Adj -via n Adj -via 2-via routing 1 n j n 3 n 1 n 2 Adj -via Adj -via Bumped seg. Adj -via Adj -via n n 4-via routing 3-via routing 1 1 cv n n 1 1 cv Adj -via Adj -via Finding Solution without Bumping – Use the 4-via Algorithm(Carothers,Lee,T-CS,1999) 1-via routing n 2 n 1 If 3-via path cannot be found due to obstacles If 1-via path cannot be found due to obstacles If 2-via path cannot be found due to obstacles

DFS-Based Incr. Routing Alg. Do-DFS-Routing(ni) Route-with-Bumping(ni) Cp=Get-Candidate-Paths Generate grid line in R-BB YES Route-without-Bumping(ni) All paths of Cptested? return(fail) NO YES return(succ.) solution Get-Next-Path(Cp) For each bumped net nk Do-DFS-Routing(nk) NO Route-with-Bumping(ni) YES return(succ.) Soln? YES Soln? NO Retract curr. bumping-causing Routing path NO return(fail)

Adj-via n 1 n n n 1 1 1 Adj-via Adj-via Equal distance m paths n 1 The first m paths Selecting Paths to Route Bumped Seg. Adj-via n 1 Adj-via Random m paths The randomized initial path set selection gave the best solutions in terms of both quality and runtime.

DFS-Based Incr. Routing Alg. Do-DFS-Routing(ni) Route-with-Bumping(ni) Cp=Get-Candidate-Paths Generate grid line in R-BB YES Have all path of CP tested Route-without-Bumping(ni) return(failed) NO YES return(succ.) Soln? Get-Next-Path(CP) For each bumped net nk Do-DFS-Routing(nk) NO Route-with-Bumping(ni) YES return(succ.) solution YES Soln? NO Retract previous bumping-causing routing NO return(failed)

nj n1.b-seg P1 n2.pin or obs DFS-Controlled Routing with Bump & Refit n3 nj n3..v1 n2 nj n1..b-seg n3..h1 n2..h1 n2..h2 n1 n1..b-seg Pi= i-via path is explored

nj n1.b-seg P1 P2 n2.pin or obs n2.h2 P1 n3.v1 DFS-Controlled Routing with Bump & Refit n3 nj n3..v1 n2 nj n2..h2 n3..h1 n2..h1 n2..h2 n1 n1..b-seg Pi= i-via path is explored

n3..v1 nj n1.b-seg P1 P2 n3..h1 n2.pin or obs n2.h2 P1 P1 n3.v1 obs P1 P2-P4 anc obs or anc.n1 or anc.nj DFS-Controlled Routing with Bump & Refit n3 nj n3..v1 n2 nj n2..h2 n2..h1 n2..h2 n1 n1..b-seg Pi= i-via path is explored

n3..v1 nj n1.b-seg P1 P2 n3..h1 n2.pin or obs n2.h2 P2-P3 P1 P1 n3.v1 n3.h1 P1 obs P1 P2-P4 P2-P4 obs anc obs or anc.n1 or anc.nj obs or anc.n1 or anc.nj DFS-Controlled Routing with Bump & Refit n3 nj n3..v1 n2 nj n2..h1 n2..h2 n1 n1..b-seg Pi= i-via path is explored

n3..v1 nj n1.b-seg P1 P2 n3..h1 n2.pin or obs n2.h2 P2-P3 P1 P1 n3.v1 n3.h1 P1 obs P1 P2-P4 P2-P4 obs anc obs or anc.n1 or anc.nj obs or anc.n1 or anc.nj DFS-Controlled Routing with Bump & Refit n3 nj n3..v1 n2 nj n2..h1 n2..h2 n2..h2 n1 n1..b-seg Pi= i-via path is explored

n3..v1 nj P2 n1.b-seg n2.h1 P1 P2 n3..h1 P1 n2.pin or obs n2.h2 obs P2-P3 P1 P1 n3.v1 n3.h1 P1 obs P1 P2-P4 P2-P4 obs anc obs or anc.n1 or anc.nj obs or anc.n1 or anc.nj DFS-Controlled Routing with Bump & Refit n3 nj n3..v1 n2 nj n1..b-seg n2..h1 n2..h2 n1 n1..b-seg Pi= i-via path is explored

n3..v1 nj P2 n1.b-seg n2.h1 P1 P2 n3..h1 P2 P1 n2.pin or obs n2.h2 VGL obs P2-P3 P1 P1 n3.v1 n3.h1 P1 obs P1 P2-P4 P2-P4 obs anc obs or anc.n1 or an.nj obs or anc.n1 or anc.nj DFS-Controlled Routing with Bump & Refit n3 nj n3..v1 n2 nj n2..h2 n1 Pi= i-via path is explored

Characteristics of Benchmark Circuits • Width of net 2 -15 unit • Space req. btw. nets 1 - 8 unit • Base 2x2 tile of Mcc1 benchmark is replicated with diff. cell sizes and diff. # of pins • Nets connected to pins randomly generated routed by using max 4-via routing • Experiment involved routing as many nets as possible under the constraint of 2 metal layers only routing succ. rate = efficacy of router

Experimental Results(Comparison of Failed Nets) • Unrouted nets are longer and wider when Std. and R&R used • DSR gets more compact layout by routing more and wider nets

Conclusions • New Incremental Routing Algorithm DSR • gridless routing • variable width/space • Produces significant impr. over Std. R&R • Via incr. of modified nets (3 (5) times less than R&R, 10% and 20%, respectively) • Higher routing success rate (Std.=10.8 (8.5) R&R= 4.6 (2.4) times worse) • Wire length (HPBB) of failed nets: Std. = 36.7 (6.59) R&R = 5.1 (2.15) times worse) • Degree of modification (~20% less modification than R&R) • Future Work • Tile-based approach to avoid congestion • Timing-driven DSR algorithm