ECE232: Hardware Organization and Design

ECE232: Hardware Organization and Design. Part 5: MIPS Instructions I http://www.ecs.umass.edu/ece/ece232/. Computer Organization. 5 classic components of any computer We have looked at datapaths ( adder, multiplier, … ). Keyboard, Mouse. Computer. Processor (CPU) (active). Memory

ECE232: Hardware Organization and Design

E N D

Presentation Transcript

ECE232: Hardware Organization and Design Part 5: MIPS Instructions I http://www.ecs.umass.edu/ece/ece232/

Computer Organization • 5 classic components of any computer • We have looked at datapaths (adder, multiplier, …) Keyboard, Mouse Computer Processor (CPU) (active) Memory (passive) (where programs, & data live when running) Devices Disk(where programs, & data live when not running) Input Control (“brain”) Datapath Output Display, Printer

Application (FireFox) Operating System Compiler (Unix; Windows) Software Assembler Instruction Set Architecture Hardware Processor Memory I/O system Datapath & Control Digital Design Circuit Design transistors, IC layout Instruction Set Architecture (ISA) • Key Idea: abstraction • hide unnecessary implementation details • helps us cope with enormous complexity of real systems

software instruction set hardware The Instruction Set: a Critical Interface The actual programmer visible hardware view

Von Neumann Computer • Stored Program Concept • A instruction is a string of bits • A program is written as a sequence of instructions • Instructions are stored in a memory • They are read one by one, decoded and executed • Also called Von Neumann Computer after the inventor of the stored program concept • The First Von Neumann Computer was built at the University of Manchester in 1948 • Vacuum Tube • Magnetic Drum Memory

Instruction Fetch Instruction Decode Operand Fetch Execute Result Store Next Instruction Execution Cycle Obtain instruction from program storage Determine required actions and instruction size Locate and obtain operand data Compute result value or status Deposit results in storage for later use Determine successor instruction

Processor Design Levels • Architecture (ISA) programmer/compiler view • “functional appearance to its immediate user/system programmer” • Opcodes, addressing modes, architecture registers • Implementation (µ-architecture)processor designer view • “logical structure or organization that performs the architecture” • Pipelining, functional units, caches, physical registers • VLSI Realization (chip)chip designer view • “physical structure that embodies the implementation” • Gates, cells, transistors, wires

Distinct Three Levels • Processors having identical ISA may be very different in organization. • Intel and AMD • Processors with identical ISA and identical organization may still be different • Different cache size • Different clock frequency Chapter 2: Instructions • Language of the Machine • MIPS instruction set architecture • similar to other architectures developed since the 1980's • used by NEC, Nintendo, Silicon Graphics, Sony • Design goals: maximize performance and minimize cost - reduce design time

Computer Processor (CPU) Devices Input Memory Control Datapath Output 0 8 bits of data 1 8 bits of data 2 8 bits of data 3 8 bits of data ? 8 bits of data 4 8 bits of data 5 8 bits of data 6 8 bits of data ... Program View of Memory • Memory viewed as a large, single -dimension array, with an address • A memory address is an index into array • The index points to a byte of memory - "Byte addressing" • A 32-bit machine addresses memory by a 32-bit address • Access bytes (8 bits), words (32 bits) or half-words

0x00000000 0x00000004 0x00000008 0x0000000C 0x00000010 0x00000014 0x00000018 0x0000001C 0xfffffff4 Memory 0xfffffffc Word 0 (bytes 0 to 3) 0xfffffffc Word 1 (bytes 4 to 7) Memory 4GB Max (Typically 512MB-2GB) CPU Address Bus Memory – word addressing • Every word in memory has an address • Today machines address memory as bytes, hence word addresses differ by 4 • Memory[0], Memory[4], Memory[8], … Called the “address” of a word

0 1 2 3 Aligned Not Aligned Memory Addressing • Questions for design of ISA • Read a 32-bit word as four loads of bytes from sequential byte addresses or as one load word from a single byte address? • One load • How do byte addresses map onto words? • Start from MS (Most Significant) byte or LS byte • Can a word be placed on any byte boundary? • MIPS: No Alignment: require that objects fall on address that is multiple of their size.

Addressing words: Big or Small Endian • Big Endian: address of most significant byte = word address (xx00 = Big End of word) • IBM 360/370, Motorola 68k, MIPS, Sparc, HP PA • Little Endian: address of least significant byte = word address (xx00 = Little End of word) • Intel 80x86, DEC Vax, DEC Alpha 3 2 1 0 little endian byte 0 msb lsb 0 1 2 3 big endian byte 0

Registers Computer • Once a memory is fetched, the data must be placed somewhere in CPU • Advantages of registers • registers are faster than memory • registers can hold variables and intermediate results • memory traffic is reduced, so program runs faster • code density improves (later) Processor (CPU) Devices Input Memory Control Datapath Registers Output

Registers • code for A = B + C (This is not MIPS code, It is in English) load R1,B # R1 = B load R2,C # R2 = C add R3,R1,R2 # R3 = R1+R2 store R3,A # A = R3 • Early ISAs supported a few registers (8 or less) (Intel’s X86) • Many current processors support 32 registers (MIPS) • The more registers available, the fewer memory accesses will be necessary • Registers can hold lots of intermediate values • Instructions must include bits to specify which registers to operate on • register address

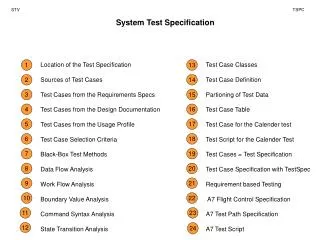

Typical Operations (little change since 1960) Data Movement Load (from memory) Store (to memory) register-to-register move input (from I/O device) output (to I/O device) push, pop (to/from stack) Arithmetic integer (binary + decimal) or FP Add, Subtract, Multiply, Divide Shift shift left/right, rotate left/right Logical not, and, or, set, clear Control (Jump/Branch) unconditional, conditional Subroutine Linkage call, return Interrupt trap, return Graphics (MMX) parallel subword ops (e.g., 4-16 bit add)

Rank instruction Average Percent executed 1 load 22% 2 conditional branch 20% 3 compare 16% 4 store 12% 5 add 8% 6 and 6% 7 sub 5% 8 move register-register 4% 9 call 1% 10 return 1% Total 96% Simple instructions dominate instruction frequency ° Top 10 80x86 Instructions • While theoretically we can talk about complicated addressing modes and instructions, the ones we actually use in programs are the simple ones • => RISC philosophy