TMS320 C6000

Instruction Set. TMS320 C6000. Dr. Naim Dahnoun, Bristol University, (c) Texas Instruments 2004. ADD .L1 A0, A1, A2. ADD .L2 -5 , B3, B4. ADD .L1 A2, A3, A5:A4. ADD .L1 A2, A5:A4 , A5:A4. ADD .L2 3 , B9:B8 , B9:B8. 'C 6xx Instruction Set - Operands.

TMS320 C6000

E N D

Presentation Transcript

Instruction Set TMS320C6000 Dr. Naim Dahnoun, Bristol University, (c) Texas Instruments 2004

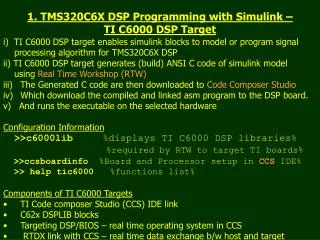

ADD .L1 A0, A1, A2 ADD .L2 -5, B3, B4 ADD .L1 A2, A3, A5:A4 ADD .L1 A2, A5:A4, A5:A4 ADD .L2 3, B9:B8, B9:B8 'C6xxInstruction Set - Operands

'C6xxInstruction Set - Cross Path ADD .L2xA0,A1,B2 MPY .M1xA0,B6,A9 SUB .S1xA8,B2,A8 ADD .L1xA0,B0,A2 LDW .D1T2 *A0,B5 STW .D2T1A5,*B0

'C6xxInstruction SetParallel Operation L1 S1 M1 D1 L2 S2 M2 D2 ADD .L2xA0,A1,B2 | |MPY .M1xA0,B6,A9 SUB .S1xA8,B2,A8 ADD .L1xA0,B0,A2 LDW .D1T2 *A0,B5 || STW .D2T1A5,*B0

Logical Arithmetic ANDCMPEQ (=)CMPGT (>)CMPLT (<)NOTORSHL (<<)SHR (>>)SSHLXOR ABSADDADDAADDKADD2MPYMPYHNEGSMPYSMPYHSADDSATSSUBSUBSUBASUBCSUB2ZERO Data Mgmt LDB/H/WMVMVCMVKMVKLMVKHMVKLHSTB/H/W Bit Mgmt Program Ctrl CLREXTLMBDNORMSET BIDLENOP Note: Refer to the 'C6000 CPU Reference Guide for more details. 'C62xInstruction Set (by category) Aritmetica di saturazione Se utilizzo la classica aritmetica di arrotondamento quando, ad esempio in un procedimento di incremento di colore, giungo al limite di rappresentazione di un dato un ulteriore incremento determina un overflow con il numero che raggiunge erroneamente il limite opposto. Quando io sommo invece ad esempio due valori a 32 bit che raggiungono un valore che eccede i limiti di rappresentazione avrei semplicemente bisogno di indicare che ho raggiunto il valore massimo rappresentabile. Questo è un evento particolarmente frequente in applicazioni multimediali (ad esempio nei valori di colore dei pixel) e l’aritmetica di saturazione serve appunto a questo. Two 16-Bit Integer Adds on Upper and Lower Register Halves if (cond) {((lsb16(src1) + lsb16(src2)) and FFFFh) or ((msb16(src1) + msb16(src2)) << 16) -> dst} else nop Integer Addition Using Addressin Mode Integer Addition Using Signed 16-Bit Constant Signed or Unsigned Integer Multiply 16 lsb x 16 lsb Signed or Unsigned Integer Multiply 16 msb x 16 msb Conditional Integer Subtract and Shift Used for Division if (cond) {if (src1 – src2 >= 0) ( (src1–src2) << 1) + 1 -> dst else src1 << 1 -> dst} else nop

.L Unit .S Unit ABSADDANDCMPEQCMPGTCMPLTLMBDMVNEGNORM ADDADDKADD2ANDBCLREXTMVMVCMVKMVKLMVKH NOTORSADDSATSSUBSUBSUBCXORZERO MVKLHNEGNOT ORSETSHLSHRSSHLSUBSUB2XORZERO .D Unit ADDADDALDB/H/WMVNEG STB/H/WSUBSUBAZERO .M Unit MPYMPYH SMPYSMPYH Other NOP IDLE 'C62x Instruction Set (by unit) TMS320C62x/C64x/C67x Fixed-Point Instruction Set Note: Refer to the 'C6000 CPU Reference Guide for more details.

.L Unit ABSADDANDCMPEQCMPGTCMPLTLMBDMVNEGNORM NOTORSADDSATSSUBSUBSUBCXORZERO ADDSPADDDPSUBSPSUBDPINTSPINTDPSPINTDPINTSPTRUNCDPTRUNCDPSP .S Unit ADDADDKADD2ANDBCLREXTMVMVCMVKMVKLMVKH NEGNOT ORSETSHLSHRSSHLSUBSUB2XORZERO ABSSPABSDPCMPGTSPCMPEQSPCMPLTSPCMPGTDPCMPEQDPCMPLTDPRCPSPRCPDPRSQRSPRSQRDPSPDP .M Unit MPYMPYHMPYLHMPYHL SMPYSMPYH MPYSPMPYDPMPYIMPYID 32-Bit Integer Multiply – Result Is Lower 32 Bits .D Unit ADDADDAB (B/H/W)ADDADLDB (B/H/W)LDDWMV NEGSTB (B/H/W) SUBSUBAB (B/H/W) ZERO No Unit Used NOP IDLE 32-Bit Integer Multiply – Result Is Lower 64 Bits Note: Refer to the 'C6000 CPU Reference Guide for more details. ' C67x: Superset of Floating-Point (by unit)

Control Registers Interrupt Control Instruction Fetch Instruction Dispatch Emulation Advanced Instruction Packing AdvancedEmulation Instruction Decode Registers (A0 - A15) Registers (B0 - B15) Registers (A16 - A31) Registers (B16 - B31) L1 S1 M1 D1 D2 M2 S2 L2 + + X + + X + + x x + + + x + + x + + + x x + + X X + + x x + + ‘C62x: Dual 32-Bit Load/Store ‘C64x: Dual 64-Bit Load/Store ‘C67x: Dual 64-Bit Load/32-Bit Store Superset of Floating-Point

Dual/Quad ArithABS2ADD2ADD4MAXMINSUB2SUB4SUBABS4 Bitwise LogicalANDN Shift & MergeSHLMBSHRMB Load ConstantMVK (5-bit) Data Pack/UnPACK2PACKH2PACKLH2PACKHL2PACKH4PACKL4UNPKHU4UNPKLU4SWAP2/4 Dual ArithmeticADD2SUB2 Bitwise LogicalANDANDNORXOR Address Calc.ADDAD Mem AccessLDDWLDNWLDNDWSTDWSTNWSTNDW Load ConstantMVK (5-bit) MultipliesMPYHIMPYLIMPYHIRMPYLIRMPY2SMPY2DOTP2DOTPN2DOTPRSU2DOTPNRSU2DOTPU4DOTPSU4GMPY4XPND2/4 Dual/Quad ArithSADD2SADDUS2SADD4 Bitwise LogicalANDN Shifts & MergeSHR2SHRU2SHLMBSHRMB Data Pack/UnPACK2PACKH2PACKLH2PACKHL2UNPKHU4UNPKLU4SWAP2SPACK2SPACKU4 ComparesCMPEQ2CMPEQ4CMPGT2CMPGT4 Branches/PCBDECBPOSBNOPADDKPC AverageAVG2AVG4 ShiftsROTLSSHVLSSHVR Bit OperationsBITC4BITRDEALSHFL MoveMVD 'C64x:Superset Fixed-Point of ‘C62x .S .L .D .M

Architecture TMS320C6000 Dr. Naim Dahnoun, Bristol University, (c) Texas Instruments 2004

Memory External Memory Internal Buses PERIPHERALS .D1 .D2 .M1 .M2 Regs (A0-A15) Regs (B0-B15) .L1 .L2 .S1 .S2 Control Regs CPU 'C6x - System Block Diagram

‘C67x can perform 64-bit data loads. ‘C6x - Internal Buses VLIW Read Write

512 32/64 32/64 32/64 32/64 32/64 'C6x - System Block Diagram

Memory size per device LINK: TMS320C6000 DSP Generation

‘C6x - Family Part Numbering Ex = TMS320 L C62 01 PKG A 200 • TMS320 = TI DSP • L = Place holder for voltage levels • C6 = C6x family • 2 = Fixed-point core • 01 = Memory/peripheral configuration • PKG = Pkg designator (actual letters TBD) • A = -40 to 85C (blank for 0 to 70C) • 200 = Core CPU speed in Mhz

Architecture • Links: • C6711 data sheet: tms320c6711.pdf • C6713 data sheet: tms320c6713.pdf • C6416 data sheet: tms320c6416.pdf • User guide C6xx: spru189f.pdf • Errata: sprz173c.pdf