NEMS Devices OPPORTUNITIES AND CHALLENGES

380 likes | 685 Vues

Adrian Ionescu Nanolab , EPFL Switzerland. NEMS Devices OPPORTUNITIES AND CHALLENGES. Goal of this talk…. Prove that energy efficient nanolectronics is a must for the future…. … and NEMS is a potential key enabling low power technology. Switch made for performance….

NEMS Devices OPPORTUNITIES AND CHALLENGES

E N D

Presentation Transcript

Adrian Ionescu Nanolab, EPFL Switzerland NEMS Devices OPPORTUNITIES AND CHALLENGES

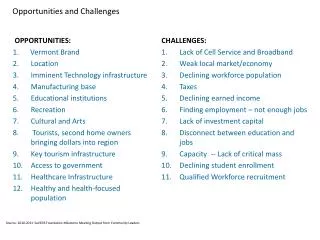

Goal of this talk… • Prove that energy efficient nanolectronics is a must for the future… • … and NEMS is a potential key enabling low power technology.

Switch made for performance… Source: Heike Riel, IBM.

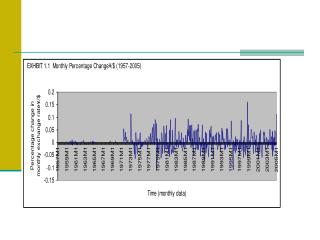

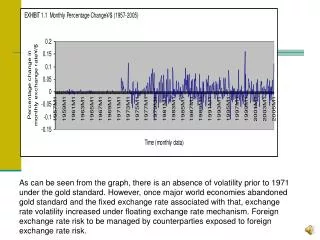

… not for energyefficiency 1E+03 Active Power Density • Power crisis in nanoelectronics • Leakage power dominates in advanced technology nodes. • VTscaling saturated by 60mV/declimit, voltage scaling slowed. 1E+02 1E+01 1E+00 1E-01 1E-02 1E-03 Passive Power Density 1E-04 1E-05 0.01 0.1 1 Power Density (W/cm2) Gate Length (μm) Source: B. Meyerson (IBM) Semico Conf., January 2004

Today’scomputing: energy/bit • What matters: • energy / computed bit • scaling • systemability • system level metrics prevail over device level • Integratedapproach for energy/bit at system level: • Switch • Memory • Interconnects • Architecture • Embedded Software

Averagesubthreshold swing VG @ VD=Vdd (mV/decade)

Subthermalswitches • A fundamental issue? • nlessthan (kT/q)ln10 • # injection in the channel • Tunnel FETs • Impact Ionization MOS • mlessthan1 • active gate devices: • NEM relay or NEMFET • negative capacitance

Nano-Electro-Mechanical (NEM) Devices • NEM switch • NEM memory • NEM resonators

Electro-mechanical info processing • as a multi-state logic, with the logic states dictated by a spatial configuration of movable objects • as vibrational modes of mechanical elements, based upon waves. • as a sensed or transduced signal operation.

NEMS simulation and modeling Source: G. Li et al, Urbana-Champaign.

NEM relay as subthermalswitch • Advantages: • - zero Ioff(zero static power). • - abrupt transition between off and on states. • (Unwanted?) feature of NEM switch: • - hysteresis due to different values of pull-in, Vpi (off-on transition) and pull-out, Vpo (off-on transition) voltages. Pull-in voltage:

MEMS foundry CMOS Si Substrate MEMS processintegration • For low cost & high performance, post-CMOS integration is desirable. • Thermal process budget is constrained for MEMS fabrication: surface micromachining is low T Source: T.J. King.

Electro-mechanical design 3-terminal relay: Stanford 2-terminal relay: EPFL 4-terminal relay: UC Berkeley

MEM logicrelay Nice but large (10’s micrometer) size! Scalable? Source: V. Pott, T.J. King, UC Berkeley.

Metal NW relays Nice, small size! Ioff excellent But voltage large: > 10V Scalable? W. W. Jang et al, Appl. Phys. Lett., 92(10), 103110, 2008.

Relay-based IC design • CMOS to real logic mappping 100x lessenergy per half-adder Relay technology F. Chen et al, ICCAD 2008.

Comms: energy per useful bit Energy / useful bit = transmit energy + transmitted energy + receive energy Role of MEMS/NEMS in low power communications? 10 pJ @ 2m ~1000 less than SoA = signal processing + front-end + sleep (“scan”) mode = signal processing + front-end PHY, MAC, NETW

First MEMS memory • B. Halg, "On a micro-electro-mechanical nonvolatile memory cell", IEEE Transactions on Electron Devices, Vol. 37, Iss. 10, 1990. • thinmicromachined • bridge elastically deformed: • two stable mechanical • states : “0” and “1” • MOS process: Si02 layer bridge covered by a 2nm thin Cr • state of the bridge changed using electrostatic forces • read out by sensing the capacitance • Size: ~hundreds mm2 • Actuation voltage: > 40V

Bistable NEM NV memorycell Y. Tsuchiya, K. Takai, N. Momo, T. Nagami, H. Mizuta, S. Oda, "Nanoelectromechanical nonvolatile memory device incorporating nanocrystalline Si dots", Journal of Applied Physics, 100, 2006.

NEMORY cell concept (1) • W.Y. Choi; H. Kam; D. Lee, J. Lai, T.-J. King Liu, "Compact Nano-Electro-Mechanical Non-Volatile Memory (NEMory) for 3D Integration", Technical Digest of IEEE International Electron Devices Meeting, IEDM 2007. • Nano-Electro-Mechanical NV memory • RWL as a top electrode • BL as a movable mechanical beam:information stored as BL position • ONO stack for charge storage • WWL as a lower electrode

NEMORY cell concept • NEMory cell operation is based on the hysteretic behavior of a mechanical gap-closing actuator. • Charge in the ONO layer is used to shift the hysteresis curves by Voffset, to achieve bistability at 0 V (VBL-WWLVBL - VWWL), thus enabling non-volatile storage.

FinFACT –switch & memory J.W. Han, Jae-HyukAhn, Min-Wu Kim, Jun-Bo Yoon, and Yang-Kyu Choi, "MonolithicIntegration of NEMS-CMOS with a Fin Flip-flop Actuated Channel Transistor (FinFACT)", IEDM 2009. Principle: laterallymovable (suspended) silicon FIN, bistable & sensed by transistor current flow.

FinFACT (2) • Depending on design (width) canbeusedboth as NV (ROM) or SRAM. • Trade-off between the endurance and retention.

CNT-basedmemorycell J.E. Jang et al, "Nanoscale memory cell based on a nanoelectromechanical switched capacitor", Nature Nanotechnology, Vol. 3, Jan. 2008, pp. 26-30. NEM switched capacitor structure based on vertically aligned MW CNTs • - Capacit. of CNT NEM DRAM cell (diameter=60 nm; length=1.6 mm; SiNx,=40 nm): value of 0.59 fF with available potential of 2.4 mV for bit line sensing in a conventional DRAM design. • 15 fF and 60–80 mV (Gbit DRAM) possible by the integration of high-k (not shown) • voltages > 14V

NEMS memory figures of merit • comparable cell area • scalable/comparable operation voltages • lowest program/erase energy:sub-10-16 J/bit.

NEM resonators • Probably the most promising family of RF M/NEMS. • Embedding full equivalent circuit functions (RLC) with very high-Q and voltage tuning (possible replacement of quartz). • Applications: oscillators, mixing, filtering, sensing. Resonant body transistor Passive MEMS resonator 26 Adrian Ionescu, GRC 2012

Theirscaling… • Frequency, mass, Q mass & force detection • nm SOI-CMOS technology integrationdensity, complexity Fully-depleted RB-FET: 0.5 µm x 0.25 µm x 10 µm Nanowire RB-FET: 40 nm x 40 nm x 2 um NW-FET body 400 nm

Low power characteristics • Tunableoperation point: • Trade-off: gain versus power. • Experiment: resonancefromstrong to weak inversion. • nWstatic power consumption in weak-inversion (PDC < PAC ). S. T. Bartsch, A.M. Ionescu, IEDM 2010.

Vibrating body transistors • Double-gate (in-plane) VB-FET resonator: transistor detection improves output signal by more than +30dB. Transistor Capacitive D. Grogg et al, IEDM 2008.

Full circuit functions… • Transistor-basedhomodyne / heterodynemixing. • Mixingcoupled to mechanical motion. • Signal-to-background improvement. • Applications: VHF mixer-filter, closed-loop configurations. Mixer output [a.u.] GateVotlage[V] Imix ~ gm Frequency [MHz] Cc-Beam: 0.15 x 0.2 x 3 µm3 f0=78 MHz, Q=1100 S.T.Bartsch et al, ACS Nano 2011.

Ultra-scaled single-NEM radio • Highly sensitive integratedsensorarrays (~10-100 attogram) • Ultra miniaturized single-device radios (RF front ends)

Vibrating body CNT FET • Device concept: • SW CNT instead of Si • fres ~100MHz-1GHz • strongpiezores. Effect 2xf • DG, 100nm airgap • By resist-assisted DEP • (>107CNTs/cm2) A.M. Ionescu, IEDM 2011 Adrian Ionescu 32 32 32 Adrian Ionescu, GRC 2012

Nano-scale active mass balance Source: Ji Cao, EPFL.

Summary (1) • Energy efficient devices: a must for the future! • Challenges: • Relays • scaling of: • gaps & size • operation voltage • reliability of contacts & packaging • dedicated IC design • Resonators • analog/RF & sensing NEMS

Summary (2) NEM memory: • exploit the. electromechanical hysteresis of movable structures by a gap closing Storage layer: specific purpose for shifting the hysteresis (NEMory, Oda’s memory, SG-FET)! • excellent co-integration with silicon CMOS. Low temperature processing, BEOL (3D-) integration possible, low cost. • Low voltage operation possible, limits ~1V • Program/erase & read times: <10ns • energy efficiency: less than 10-16 J/bit in NEMory & SBM. • Trade-off between endurance & retention in FIN-FACT. • Robust in high temperature and radiation environments. • CNT-based memory: immature • Promising for embedded memory applications