EE 587 SoC Design & Test

The System-on-a-Chip (SoC) revolution introduces new challenges in design and testing, particularly regarding power dissipation. Traditional DFT techniques focused on parameters like area overhead and fault coverage, but modern low-power devices force engineers to prioritize power management during testing. With increased switching activity in test modes and the rise of at-speed testing, managing heat becomes complex. Built-In Self-Test (BIST) methods and scan-based architectures provide solutions but often result in higher energy consumption. Effective test scheduling and low-power techniques are essential for successful SoC testing.

EE 587 SoC Design & Test

E N D

Presentation Transcript

EE 587SoC Design & Test Partha Pande School of EECS Washington State University pande@eecs.wsu.edu

Testing & Power • THE SYSTEM-ON-A-CHIP(SoC) revolution brings out new challenges for both the design and test engineers, especially in the area of power dissipation • Traditionally, test engineers evaluated the DFT techniques according to various parameters: area overhead, fault coverage, test application time, test development effort, and so forth • But now, the recent development of complex, high-performance, low-power devices implemented in deep-submicron technologies creates a new class of more sophisticated electronic products, which makes power management a critical parameter that test engineers cannot ignore during test development

Background • Test efficiency correlates with toggle rate • In the test mode the switching activity of all nodes is often several times higher than that during normal operation • Test engineers use parallel testing in SoCs to reduce the test application time • might result in excessive power dissipation • the DFT circuitry designed to reduce the test complexity is often idle during normal operation but might be extensively used in the test mode • Successive functional input vectors applied to a given circuit during system mode have a significant correlation. In contrast, the correlation between consecutive test patterns can be low

Background • Current trend in circuit design toward circuit miniaturization prevents the use of special cooling equipment for removing excessive heat during test • The growing use of at-speed testing for identifying slow chips no longer permits compensating for increased power dissipation by reducing test frequency • In the past, tests typically ran at lower rates than a circuit’s normal clock rate, because they needed to cover only stuck-at faults. Now, aggressive timing makes it essential for tests to identify slow chips through delay testing, which manufacturers use to performance certify cores for use in SoC designs

Power & BIST • Modern design and package technologies make external testing increasingly difficult, and BIST has emerged as a promising solution to the VLSI testing problem • BIST is a DFT methodology aimed at detecting faulty components in a system by incorporating test logic on chip. • In BIST, an LFSR generates test pattern • LFSR-generated tests tend to take longer to reach acceptable levels of fault coverage, which increases the total energy consumption • Test vectors applied at nominal operating frequency will have a higher average power dissipation than normal mode. This is because in normal mode, successive functional input vectors applied to a given circuit have significant correlation; the consecutive vectors of an LFSR generated test sequence have a lower correlation.

SCAN • Scan-based, self-test architectures are popular because of their low impact on performance and area • These scan-based architectures are expensive because each test pattern requires a power-consuming shift operation to provide test patterns and evaluate test response • To meet specified power limits during test and avoid system destruction, it is important to reduce power dissipation during scan shifting.

Built-In Self-Test (BIST) BIST Controller Linear feedback shift register (LFSR) Pseudo-random patterns Circuit under test (CUT) Circuit responses Multiple input signature register (MISR) Clock

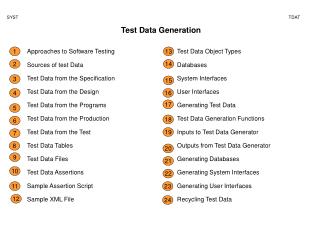

Functional inputs: Functionally meaningful signals Generated by circuitry Restricted set of inputs May have been optimized to reduce logic activity and power Test vectors: Functionally irrelevant signals Generated by software to test faults Can be random or pseudorandom May be optimized to reduce test time; can have high logic activity May use testability logic for test application Functional Inputs vs. Test Vectors

Reducing Test Power 1 V1 V2 V3 V4 V5 3 4 V1 V2 V3 1 1 0 0 0 1 0 1 0 0 1 0 1 0 1 1 0 1 1 1 3 1 2 3 2 1 V4 V5 10 input transitions 2 Traveling salesperson problem (TSP): Find the shortest distance closed path (or cycle) to visit all nodes exactly once. V1 V3 V5 V4 V2 1 0 0 0 1 1 1 0 0 0 1 1 1 0 0 1 1 1 1 0 5 input transitions

Low Power BIST • Low-power BIST techniques • Test Scheduling • Low-power test pattern generation • Toggle suppression • Vector filtering • Circuit partitioning

A System Example: ASIC Z* RAM 2 Time=61 Power=241 RAM 3 Time=38 Power=213 Random logic 1, time=134, power=295 Random logic 2, time=160, power=352 ROM 1 Time=102 Power=279 ROM 2 Time=102 Power=279 RAM 4 Time=23 Power=96 RAM 1 Time=69 Power=282 Reg. file Time = 10 Power=95 *Y. Zorian, “A Distributed Control Scheme for Complex VLSI Devices,” Proc. VLSI Test Symp., April 1993, pp. 4-9.

Test Scheduling • Distributed BIST control scheme • Schedule the execution of every BIST element to keep the power dissipation under specified limits • The package limit of the ASIC is 900 mw • If we run parallel BIST then the power dissipation is 2.332 w • BIST scheduling is must

Grouping & Ordering of blocks • If the BIST execution is to be performed in multiple stages, then creating groups of blocks to be executed in each stage and proper sequencing of such stages is necessary • Physical distribution of the blocks on the floor plan need to be considered • A group of blocks execute BIST in a single stage • BIST power dissipation of a group has to be less than the device limit • Blocks in a group have to be physically adjacent on a floor plan

Distributed BIST Control • each matrix element Bij represents a block in the device • each row i represents a single BIST execution stage • j represents the number of a block in a given stage • the order of the rows represents the sequence of BIST execution stages

BIST Control Architecture • Centralized Control • Control lines that connect the controller to the local BRCs increases linearly with the number of BRC • For a SoC with small number of blocks, a centralized BIST controller is possible • For big SoCs distributed control is preferred • The distributed control architecture will be composed of a set of control elements, to be called Scheduled BIST Resource Interface Controllers (SBRICs).

Distributed BIST Control • An SBRIC is a customized finite state machine which contains five states. It provides BRC coordination along with Test response collection and transfer capabilities • An SBRIC communicates with its associated BRCs using the uniform interface protocol

Low Power Test Pattern Generation • Dual-Speed LFSR • Decrease the circuit’s overall internal activity by connecting inputs that have elevated transition densities to the slow-speed LFSR

Low Power SCAN • Two sources of power dissipation during scan testing • Power dissipated when the outputs of logic gates in the circuit switch, which is referred to as “logic power” • power dissipated in the clock tree each time the clock makes a transition, which is referred to as the “clock power” • Consider a core that has multiple scan chains. We generate and order the test set in such a way that some of the scan chains can have their clock disabled for portions of the test set • When the clock is disabled for 4 of the scan chains, the contents of those scan chains remain constant which reduces circuit switching hence reducing logic power. Moreover, the clock power is reduced by a factor of two because half of the scan elements in the circuit are not clocked • For example, suppose a core has 8 scan chains and 300 test vectors. If we can generate and order the test vectors in such a way that we do not need to clock 4 of the scan chains for 200 of the test vectors, then we can reduce the total power (both logic power and clock power) during test by roughly 33%

Low Power SCAN • The only hardware modification required for the proposed scheme is to add the capability to disable the clock for a subset of the scan chains • scan chains in the core are divided into two sets, set A and set B • An extra “disable” input is added to the core, which allows the tester to control when the clock is disabled to the scan elements in set B • For Mux-D type scan elements, the system clock is gated and controlled by disable so that when disable is activated, the scan chains in set B will neither shift in scan mode, nor capture in system mode.

Low Power SCAN • Most switching activity in the circuit occurs during scan shifting • Average and peak power dissipation can be reduced by reducing the switching activity during scan operation • Gated Clock scheme • Reduce the clock frequency on the scan cells during shift operations without increasing the test time • A clock whose speed is half of the normal speed is used to activate one half of the scan cells during one clock cycle of the scan operation. During the next clock cycle, the second half of the scan cells is activated by another clock whose speed is also half of the normal speed.

Weighted Switching Activity (WSA) • The weighted switching activity (WSA) is defined as the number of toggles of a node multiplied by its capacitance • The consumed energy directly corresponds to the WSA

Toggle Suppression • During shifting the output of each scan element is highly active, causing a large power consumption • Modify the scan cells in such a way that the module under test (MUT) inputs remain unchanged during a shift operation • only if the test is disabled (t=0), the NOR gate is transparent

D DFF D’ mux SI SE Low Power Scan Flip-Flop SO SO D 1 0 DFF mux D’ SI SE Scan FF cell Low power scan FF cell

Vector Filtering BIST • it is possible to reduce the circuit activity by simply observing the pseudo-random test sequence provided by the LFSR and analyzing the detection capability of each vector. • Filter out nondetecting subsequences of a pseudorandom test set generated by an LFSR • From fault simulation, it can be easily verified that not all patterns in a pseudo-random test sequence detects faults in the circuit.

Vector Filtering in Scan-based Test • The energy consumption caused by switching the clock tree and by shifting patterns into the scan path can be minimized if the shift clock is enabled during essential patterns only • Essential patterns are those patterns that contribute to increase the fault coverage • For all other patterns the clock tree is disabled so that the patterns generated by the TPG are not shifted into the scan path.

Circuit Partitioning • Partition the original circuit into two structural sub circuits so that two different BIST sessions can successively test each sub circuit • the average power as well as the peak power consumption are minimized • only one part of the circuit may be activated in a given time interval, while all the nodes in the circuit may be activated during the same time interval in a standard BIST scheme • the total energy consumption during BIST is also reduced since the test length required to successively test the two sub circuits is never greater than the test length for the original circuit (to reach the same or sometimes a better fault coverage).

Final Words • There are several relevant criteria to consider when selecting solutions for minimizing test power • Fault Coverage and test time, must remain unaltered by the implemented technique • The area overhead from hardware modifications must be low • The techniques must maintain circuit performance