System Architecture and Von Neumann Principles

E N D

Presentation Transcript

1-2 – Central Processing Unit (c) 2018

Central Processing Unit (c) 2018

Introduction (c) 2018

System architecture • How all the different hardware components connect together • Central Processing Unit (CPU) consists of the following: • Arithmetic Logic Unit (ALU) • Control Unit (CU) • Clock • Bus • Watch http://tiny.cc/systemarchitecture from BBC Bitesize for an overview of the system architecture (c) 2018

Von Neumann Architecture (c) 2018

Textbook reading Read pages 6-7 of Chapter 1 – Computer Systems from The Ultimate GCSE Computer Science Textbook (c) 2018

Von Neuman Architecture 1 • John von Neumann • Mathematician in the 1940s • Identified that data and programs could be stored in the same memory • Only one set of RAM required for both data and programs • Other architectures also used in many smartphones • eg Harvard architecture (c) 2018

Von Neumann Architecture 2 • John von Neumann described system architecture as comprising: CPU ControlUnit Input Output Arithmetic Logic Unit Memory (c) 2018

Arithmetic Logic Unit - ALU • Part of CPU • Carries out arithmetic calculations • Addition • Subtraction • Shifts (multiplication and division) • Carries out logical operations • AND • OR • NOT • Less Than < • Greater Than > 5 + 6 = 11 if x > y (c) 2018

Control Unit - CU • Part of CPU • Manages the execution of instructions • Ensures all components perform tasks at the correct time • Responsible for the fetch-execute cycle • Analogy: a conductor for an orchestra (c) 2018

Clock • A signal to synchronise tasks • Clock cycle is known as a tick • Each cycle has • high state • Low state high one cycle (tick) low Tick Tick (c) 2018

Bus • System bus connects: • CPU • Memory • Input/Output • Three buses: • control bus (control signals) • address bus (memory addresses) • data bus (instructions and data items) (c) 2018

Fetch-Execute cycle (c) 2018

Textbook reading Read page 8 of Chapter 1 – Computer Systems from The Ultimate GCSE Computer Science Textbook (c) 2018

Fetch-execute cycle • During one cycle: • Fetch next instruction from memory • Decode instruction • Execute the instruction STORE 13 01011101 (c) 2018

http://tiny.cc/fetchexecute (3:12 to 4:42) - Fetch-Execute Cycle

Registers used in Fetch-execute cycle • Registers • areas of memory in the CPU • hold data and memory addresses • Program counter- PC • address of next instruction in memory • (also known as instruction address register – IAR) • Memory address register– MAR • address of instruction during fetch phase • OR address to retrieve data from during execute phase • Memory data register – MDR • current data that has been • fetched from memory • OR is about to be stored in memory • (also known as the memory buffer register – MBR) • Current instruction register – CIR • instruction to be executed • Accumulator – ACC • result of the current calculation CPU P C M A R C U C I R M D R A L U A C C (c) 2018

http://tiny.cc/fetchexecutefull - detailed explanation of Fetch-Execute Cycle

Fetch stage - 1 • The address in memory of the next instruction is already stored in the Program Counter (PC) RAM CPU Address Bus P C - M A R - C U Data Bus 0 C I R - M D R - A L U Control Bus A C C - (c) 2018

Fetch stage - 2 • The address in the Program Counter (PC) is copied to the Memory Address Register (MAR) • The Control Unit sends the contents of the Memory Address Register to RAM RAM CPU Address Bus P C - M A R - C U Data Bus 0 0 C I R - M D R - A L U Control Bus A C C - (c) 2018

Fetch stage - 3 • The instruction is now retrieved from memory and sent along the data bus to the Memory Data Register(MDR) • The instruction is then copied from the Memory Data Register (MDR) to the Current Instruction Register (CIR) • Finally the value of the Program Counter is increased by one ready for the next instruction after the fetch execute cycle RAM CPU Address Bus P C - M A R - C U Data Bus LOAD 4 0 1 0 C I R - M D R - LOAD 4 A L U Control Bus A C C - (c) 2018

Decode stage • The instruction in the Memory Data Register (MDR) is decoded by the Control Unit (CU) • LOAD is recognised as the op-code (instruction) and 4 as the operand (memory location) RAM CPU Address Bus P C - M A R - C U Data Bus 1 0 C I R - M D R - 4 LOAD 4 LOAD 4 LOAD A L U Control Bus A C C - (c) 2018

Execute stage - 1 • The memory address is copied from the CIR to the Memory Address Register (MAR) • It is then passed along the address bus to main memory (RAM) RAM CPU Address Bus P C - M A R - C U Data Bus 1 0 4 C I R - M D R - 4 4 LOAD 4 LOAD 4 LOAD A L U Control Bus A C C - (c) 2018

Execute stage - 2 • The data at that memory address is passed to the Memory Data Register (MDR) RAM CPU Address Bus P C - M A R - C U Data Bus 1 4 C I R - M D R - LOAD 4 LOAD 4 A L U Control Bus A C C - 4 25 (c) 2018

Execute stage - 3 • The instruction from the Current Instruction Register is then executed on the data in the MDR • In this example, 25 is loaded from the Memory Data Register (MDR) to the Accumulator (ACC) RAM CPU Address Bus P C - M A R - C U Data Bus 1 4 C I R - M D R - 25 25 LOAD 4 LOAD A L U Control Bus A C C - (c) 2018

Cycle completed • The first fetch-execute cycle is now completed • With a 2 GHz processor, that took just half a billionth of a second (c) 2018

Textbook reading Read pages 9-10 of Chapter 1 – Computer Systems from The Ultimate GCSE Computer Science Textbook (c) 2018

Cycle 2 • The clock can now tick again for the next fetch-execute cycle (c) 2018

Fetch stage - 1 • The address in memory of the next instruction is already stored in the Program Counter (PC) RAM CPU Address Bus P C - M A R 4 C U Data Bus 1 C I R LOAD 4 M D R 25 A L U Control Bus A C C 25 (c) 2018

Fetch stage - 2 • The address in the Program Counter (PC) is copied to the Memory Address Register (MAR) • The Control Unit sends the contents of the Memory Address Register to RAM RAM CPU Address Bus P C - M A R 4 C U Data Bus 0 1 C I R LOAD 4 M D R 25 A L U Control Bus A C C 25 (c) 2018

Fetch stage - 3 • The instruction is now retrieved from memory and sent along the data bus to the Memory Data Register(MDR) • The instruction is then copied from the Memory Data Register (MDR) to the Current Instruction Register (CIR) • Finally the value of the Program Counter is increased by one ready for the next instruction after the fetch execute cycle RAM CPU Address Bus P C - M A R - C U Data Bus 1 2 1 ADD 5 C I R LOAD 4 M D R - ADD 5 A L U Control Bus A C C 25 (c) 2018

Decode stage • The instruction in the Memory Data Register (MDR) is decoded by the Control Unit (CU) • add is recognised as the op-code (instruction) and 5 as the operand (memory location) RAM CPU Address Bus P C - M A R - C U Data Bus 2 1 C I R - M D R - 5 ADD 5 ADD 5 ADD A L U Control Bus A C C 25 (c) 2018

Execute stage - 1 • The memory address is copied from the CIR to the Memory Address Register (MAR) • It is then passed along the address bus to main memory (RAM) RAM CPU Address Bus P C - M A R - C U Data Bus 2 1 5 C I R - M D R - LOAD 4 ADD 5 5 A L U Control Bus A C C 25 (c) 2018

Execute stage - 2 • The data at that memory address is passed to the Memory Data Register (MDR) RAM CPU Address Bus P C - M A R - C U Data Bus 2 5 C I R - M D R - ADD 5 ADD 5 A L U Control Bus A C C 25 12 5 (c) 2018

Execute stage - 3 • The instruction from the Current Instruction Register is then executed on the data in the MDR • In this example, 12 is added from the Memory Data Register (MDR) to the Accumulator (ACC) RAM CPU Address Bus P C - M A R - C U Data Bus 2 5 C I R ADD 5 M D R - 12 ADD 5 ADD 12 A L U Control Bus A C C 25 25 (c) 2018

Execute stage - 4 • The calculation is carried out by the Arithmetic Logic Unit (ALU) • The result of the calculation is stored in the Accumulator (ACU) RAM CPU Address Bus P C - M A R - C U Data Bus 2 5 C I R ADD 5 M D R - 12 ADD 5 A L U Control Bus A C C 25 25 37 12 ADD (c) 2018

Textbook reading Read pages 11-14 of Chapter 1 – Computer Systems from The Ultimate GCSE Computer Science Textbook (c) 2018

Activity – fetch-execute cycle Follow this animation from www.tiny.cc/fetchexecuteanimation (requires flash)

Activity – fetch-execute cycle • Complete question 2 of the activity on the fetch-execute cycle from The Ultimate GCSE Computer Science Textbook (c) 2018

Performance of the CPU (c) 2018

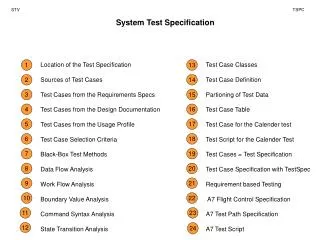

Performance of the CPU Cache Type Cache Size • Factors affecting performance of the CPU include: • Clock speed • Number of processor cores • Cache size • Cache type Cores Clock Speed (c) 2018

Textbook reading Read pages 16-18 of Chapter 1 – Computer Systems from The Ultimate GCSE Computer Science Textbook (c) 2018

Clock speed • Number of clock cycles per second • Measured in Hz • eg 3 GHz (gigahertz) = 3 billion ticks per second • more ticks = more instructions per second • Overclocking • Increasing CPU speed in the BIOS • Can cause overheating • Some processes may not complete before next instruction starts • Results in corrupted data (c) 2018

http://tiny.cc/cpuperformance - factors beyond CPU Clock Speeds that affect Performance

Number of processor cores • Core = processing unit which receives instructions and performs calculations • More cores do not make the processor faster • More cores do allow • more instructions to run at the same time • BUT only if a program or operating system support it • Performance will improve through: • parallel processing • multitasking (c) 2018

Parallel processing and multi-tasking • Parallel processing • different instructions from the same program run at the same time • more cores = more instructions from the same program running at the same time • Multitasking • instructions from many programs run at the same time • more cores = more instructions from many programs running at the same time 9 8 7 6 5 4 3 2 1 (c) 2018

Single core processor • Instructions happen one at a time in sequence • for 1 Hz, this would be up to 1 instruction every second: 2 3 4 5 6 7 8 9 1 (c) 2018

Dual core processor • With a multitasking operating system or software that supports parallel processing: • two instructions can be run in parallel at a time • for 1 Hz, this would be up to 2 instructions per second: • what happened with the 9th instruction? 9 7 5 1 3 8 6 4 2 (c) 2018

Quad core processor • We already know: with a multitasking operating system or software that supports parallel processing: • two instructions can be run in parallel at a time • for 1 Hz, this would be up to 2 instructions per second • BUT without a multitasking operating system or without software that supports parallel processing: • only one core will be used • for 1 Hz, this would be up to 1 instruction every second, not 4 instructions per second: 2 3 4 5 6 7 8 9 1 (c) 2018

http://tiny.cc/cores - How the Number of Cores affects Performance