Designing State Machines SQRT controller

Designing State Machines SQRT controller. Lecture L9.2a Section 9.2. SQRT Controller. Mealy and Moore Machines SQRT Controller. A canonical sequential network. A Mealy state machine. A Moore state machine. SQRTctl. Lab 8. MODULE SQRTctl

Designing State Machines SQRT controller

E N D

Presentation Transcript

Designing State MachinesSQRT controller Lecture L9.2a Section 9.2

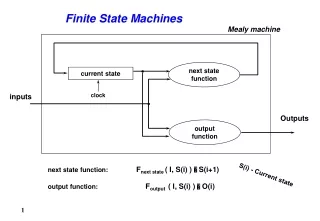

SQRT Controller • Mealy and Moore Machines • SQRT Controller

MODULE SQRTctl interface(Clk, Clear, lteflg, strt -> ald, sqld, dld, outld); TITLE 'Control Unit for square root algorithm' DECLARATIONS " INPUT PINS " Clk PIN; " clock lteflg PIN; " <= flag Clear PIN; " clear start PIN; " GCD starts when start = 1 " OUTPUT PINS " ald, sqld, dld, outld PIN; " reg load signals

Q1..Q0 NODE ISTYPE 'reg buffer'; Q = [Q1..Q0]; " 2-bit state vector " Definitions QSTATE = [Q1, Q0]; start = [0, 0]; test = [0, 1]; update = [1, 0]; done = [1, 1]; state_diagram QSTATE state start: if strt then test else start; state test: if lteflg then update else done; state update: goto test; state done: goto done;

EQUATIONS WHEN QSTATE == start then " a <- SW {ald = 1; sqld = 0; dld = 0; outld = 0;} WHEN QSTATE == test then {ald = 0; sqld = 0; dld = 0; outld = 0;} WHEN QSTATE == update then " sq <- sq + del; del <- del + 2 {ald = 0; sqld = 1; dld = 1; outld = 0;} WHEN QSTATE == done then " out <- (del - 1)/2 {ald = 0; sqld = 0; dld = 0; outld = 1;} Q.C = Clk; Q.AR = Clear; END SQRTctl