Chapter 15 Multistage Amplifiers

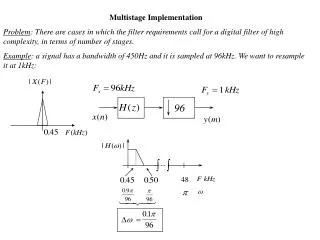

Chapter 15 Multistage Amplifiers. Microelectronic Circuit Design Richard C. Jaeger Travis N. Blalock. Chap 15 - 1. Chapter Goals. Understand analysis and design of ac-coupled multistage amplifiers including voltage gain, input and output resistances and small signal limitations.

Chapter 15 Multistage Amplifiers

E N D

Presentation Transcript

Chapter 15Multistage Amplifiers Microelectronic Circuit Design Richard C. Jaeger Travis N. Blalock Microelectronic Circuit Design McGraw-Hill Chap 15 - 1

Chapter Goals • Understand analysis and design of ac-coupled multistage amplifiers including voltage gain, input and output resistances and small signal limitations. • Understand analysis and design of dc-coupled multistage amplifiers. • Discuss characteristics of Darlington configuration and cascode amplifier. • Explore dc and ac properties of differential amplifiers. • Understand basic three-stage op amp. • Explore design of class-A, class-B, class-AB output stages. • Discuss characteristics and design of electronic current sources. • Continue understanding the use of SPICE in circuit analysis. Microelectronic Circuit Design McGraw-Hill Chap 15 - 2

AC-coupled Amplifiers: Circuit Microelectronic Circuit Design McGraw-Hill Chap 15 - 3

AC-coupled Amplifiers: Description • MOSFET M1operating in C-S configuration provides high input resistance and moderate voltage gain. • BJT Q2 in C-E configuration, the second stage, provides high gain. • BJT Q3, an emitter-follower gives low output resistance and buffers the high gain stage from the relatively low load resistance. • Bias resistors are replaced by • Input and output of overall amplifier is ac-coupled through capacitors C1 and C6. • Bypass capacitors C2 and C4 are used to get maximum voltage gain from the two inverting amplifiers. • Interstage coupling capacitors C3 and C5 transfer ac signals between amplifiers but provide isolation at dc, and prevent Q-points of the transistors from being affected. Microelectronic Circuit Design McGraw-Hill Chap 15 - 4

AC-coupled Amplifiers: Equivalent Circuits AC Equivalent Small-signal Equivalent DC Equivalent Microelectronic Circuit Design McGraw-Hill Chap 15 - 5

AC-coupled Amplifiers: Input Resistance and Voltage Gain Microelectronic Circuit Design McGraw-Hill Chap 15 - 6

AC-coupled Amplifiers: Output Resistance To find output resistance, test voltage is applied at amplifier output. Microelectronic Circuit Design McGraw-Hill Chap 15 - 7

AC-coupled Amplifiers: Current and Power Gain Input current delivered to amplifier from source is and current delivered to load by amplifier is Microelectronic Circuit Design McGraw-Hill Chap 15 - 8

AC-coupled Amplifiers: Input Signal Range • For first stage, • For second stage, • For third stage, • On the whole, Microelectronic Circuit Design McGraw-Hill Chap 15 - 9

AC-coupled Amplifiers: Methods to Improve Voltage Gain • Gain of C-S amplifier is inversely proportional to square root of drain current, so voltage gain could be increased by reducing ID1 while maintaining a constant voltage drop across RD1. Signal range could be improved by increasing current in output stage and voltage drop across RE3. • Q1 could be replaced with a FET. This could cause gain loss in third stage since gain of C-D amplifier is typically < that of a C-C stage. However, this loss could be made up by improving gain of first and second stages. Microelectronic Circuit Design McGraw-Hill Chap 15 - 10

Common-Emitter Cascade If gain is limited by interstage resistances, each stage has a gain of about -10VCC and overall gain is: If gain is limited by input resistance of transistors, it is given by: Normally as signal and power levels usually increase in each successive stage of most amplifiers. Since bo< 10VCC , this case often represents the actual limit. To achieve maximum gain, several C-E stages can be cascaded. For the final stage, For all other stages, Microelectronic Circuit Design McGraw-Hill Chap 15 - 11

Direct-coupled Amplifiers: Circuit • Bypass capacitors- C2 and C4 affect gain at low frequencies but don’t inherently prevent the amplifier from operating at dc. • Symmetrical power supplies are used to set Q-point voltages at input and output to about zero. • Alternating pnp or p-channel and npn or n-channel transistors are used from stage to stage to take maximum advantage of available power supply voltage. • Coupling capacitors in series with signal path- C1, C3, C5, and C6 are eliminated as they prevent the amplifier from providing gain at dc or very low frequencies. • Additional bias resistors in individual stages are also removed, making design less expensive. Microelectronic Circuit Design McGraw-Hill Chap 15 - 12

Direct-coupled Amplifiers: DC Analysis So, ID = 6.66. mA (which would produce 10.7 V drop across RS1 and cut off FET) or ID =5.29 mA (correct value). IB2 << ID, which is enough to pinch off M1. bF2 =150, so IC2 =1.83 mA and IB2 = 12.2 mA. IB3 << IC2, which < 0.7 V , so Q2 is in active region. Voltage at drain of M1 provides base bias for Q2 and voltage at collector of Q2 provides base bias for Q3. All transistors operate in active region irrespective of direct connection between stages. Microelectronic Circuit Design McGraw-Hill Chap 15 - 13

Direct-coupled Amplifiers: DC Analysis (contd.) bF3 = 80, so IC3 =3.94 mA and IB3 = 49.3 mA thus Q3 is in active region. There is an offset voltage of 0.4 V at output and a nonzero dc current exists in 250 W load resistor. In an ideal design, offset voltage would be zero and no dc current would appear in load. Based on Q-point values, small-signal parameters can be calculated. Microelectronic Circuit Design McGraw-Hill Chap 15 - 14

Direct-coupled Amplifiers: AC Analysis • Dc coupling requires fewer components than ac-coupling but Q-points of various stages become interdependent. • If Q-point of one stage shifts, Q-points of all other stages might also shift. • Values of interstage capacitors are higher than those in ac-coupled amplifier due to absence of bias resistors. • Overall characteristics are similar to those in ac-coupled amplifier as Q-points and small-signal parameters of transistors are similar Microelectronic Circuit Design McGraw-Hill Chap 15 - 15

Direct-coupled Amplifiers: Darlington Circuit AC Analysis: For the composite transistor, Darlington circuit behaves similar to the single transistor but has a current gain given by the product of current gains of individual transistors. DC Analysis: For bF1, bF2 >>1, VBE of composite transistor = 2 diode voltage drops. So VCE >(VBE1 + VBE2) . Microelectronic Circuit Design McGraw-Hill Chap 15 - 16

Direct-coupled Amplifiers: Cascode Circuit AC Analysis: For the composite transistor, Cascode circuit is cascade connection of C-E and C-B amplifiers, used in high gain amplifiers and high output resistance current sources. DC Analysis: For a high current gain, For forward-active operation of Q2, Microelectronic Circuit Design McGraw-Hill Chap 15 - 17

Differential Amplifiers • Differential-mode output voltage is the voltage difference between collectors, drains of the two transistors.Ground referenced outputs can also be taken from collector/drain. • Ideal differential amplifier uses perfectly matched transistors. • Differential amplifiers,also considered the C-C/C-B cascade, eliminate the bypass capacitors as well as the external coupling capacitors at the input and output of direct-coupled amplifiers. • Each circuit has two inputs. Microelectronic Circuit Design McGraw-Hill Chap 15 - 18

Bipolar Differential Amplifiers: DC Analysis Terminal currents are also equal. Both inputs are set to zero, emitters are connected together. If transistors are matched, Microelectronic Circuit Design McGraw-Hill Chap 15 - 19

Small-Signal Transfer Characteristic The current switch is a digital application of the differential amplifier. Large-signal transfer characteristic of differential amplifier is given by: Even-order distortion terms are eliminated.This increases signal-handling capability of differential pair. For small-signal operation, liner term must be dominant. Hence, we set the third-order term to be one-tenth the linear term. Microelectronic Circuit Design McGraw-Hill Chap 15 - 20

Bipolar Differential Amplifiers: DC Analysis (Example) • Problem:Find Q-points of transistors in the differential amplifier. • Given data:VCC=VEE=15 V, REE=RC=75kW, bF =100 • Analysis: Due to symmetry, both transistors are biased at Q-point (94.4 mA, 8.62V) Microelectronic Circuit Design McGraw-Hill Chap 15 - 21

Bipolar Differential Amplifiers: AC Analysis Add = differential-mode gain Acd = common-mode to differential-mode conversion gain Acc = common-mode gain Adc = differential mode to common-mode conversion gain For ideal symmetrical amplifier, Acd = Adc = 0. Purely differential-mode input gives purely differential-mode output and vice versa. Circuit analysis is done by superposition of differential-mode and common-mode signal portions. Microelectronic Circuit Design McGraw-Hill Chap 15 - 22

Bipolar Differential Amplifiers: Differential-mode Gain and Input Resistance Emitter node in differential amplifier represents virtual ground for differential-mode input signals. Output signal voltages are: Microelectronic Circuit Design McGraw-Hill Chap 15 - 23

Bipolar Differential Amplifiers: Differential-mode Gain and Input Resistance (contd.) Differential-mode gain for balanced output, is: If either vc1 or vc2 is used alone as output, output is said to be single-ended. Differential-mode input resistance is small-signal resistance presented to differential-mode input voltage between the two transistor bases. If vid =0, . For single-ended outputs, Microelectronic Circuit Design McGraw-Hill Chap 15 - 24

Bipolar Differential Amplifiers: Common-mode Gain and Input Resistance Both arms of differential amplifier are symmetrical. So terminal currents and collector voltages are equal. Characteristics of differential pair with common-mode input are similar to those of a C-E (or C-S) amplifier with large emitter (or source) resistor. Output voltages are: Microelectronic Circuit Design McGraw-Hill Chap 15 - 25

Bipolar Differential Amplifiers: Common-mode Gain and Input Resistance (contd.) Common-mode gain is given by: For symmetrical power supplies, common-mode gain =0.5. Thus, common-mode output voltage and Acc is 0 if REE is infinite. This result is obtained since output resistances of transistors are neglected. A more accurate expression is: Therefore, common-mode conversion gain is found to be 0. Microelectronic Circuit Design McGraw-Hill Chap 15 - 26

Common-Mode Rejection ratio (CMRR) • Represents ability of amplifier to amplify desired differential-mode input signal and reject undesired common-mode input signal. • For differential output, common-mode gain of balanced amplifier is zero, CMRR is infinite. For single-ended output, • For infinite REE , CMRR is limited by bomf . If term containing REE is dominant Thus for differential pair biased by resistor REE , CMRR is limited by available negative power supply. • Due to mismatches, , gives fractional mismatch between small-signal device parameters in the two arms of differential pair. Hence gmREE product is maximized. Microelectronic Circuit Design McGraw-Hill Chap 15 - 27

Analysis of Differential Amplifiers Using Half-Circuits • Half-circuits are constructed by first drawing the differential amplifier in a fully symmetrical form- power supplies are split into two equal halves in parallel, emitter resistor is separated into two equal resistors in parallel. • None of the currents or voltages in the circuit are changed. • For differential mode signals, points on the line of symmetry are virtual grounds connected to ground for ac analysis • For common-mode signals, points on line of symmetry are replaced by open circuits. Microelectronic Circuit Design McGraw-Hill Chap 15 - 28

Bipolar Differential-mode Half-circuits Direct analysis of the half-circuits yield: Applying rules for drawing half-circuits, the two power supply lines and emitter become ac grounds. The half-circuit represents a C-E amplifier stage. Microelectronic Circuit Design McGraw-Hill Chap 15 - 29

Bipolar Common-mode Half-circuits • All points on line of symmetry become open circuits. • DC circuit with VIC set to zero is used to find amplifier’s Q-point. • Last circuit is used for for common-mode signal analysis and represents the C-E amplifier with emitter resistor 2REE. Microelectronic Circuit Design McGraw-Hill Chap 15 - 30

Bipolar Common-mode Input Voltage Range For symmetrical power supplies, VEE >> VBE, and RC = REE, Microelectronic Circuit Design McGraw-Hill Chap 15 - 31

Biasing with Electronic Current Sources • Differential amplifiers are biased using electronic current sources to stabilize the operating point and increase effective value of REE to improve CMRR • Electronic current source has a Q-point current of ISS and an output resistance of RSS as shown. • DC model of the electronic current source is a dc current source, ISS while ac model is a resistance RSS. SPICE model includes both ac and dc models. Microelectronic Circuit Design McGraw-Hill Chap 15 - 32

MOSFET Differential Amplifiers: DC Analysis and Op amps with MOSFET inputs have a high input resistance and much higher slew rate that those with bipolar input stages. Using half-circuit analysis method, we see that IS = ISS /2. Microelectronic Circuit Design McGraw-Hill Chap 15 - 33

Small-Signal Transfer Characteristic MOS differential amplifier gives improved linear input signal range and distortion characteristics over that of a single transistor. Second-order distortion product is eliminated and distortion is greatly reduced. However some distortion prevails as MOSFETs are nor perfect square law devices and some distortion arises through voltage dependence of output impedances of the transistors. For symmetrical differential amplifier with purely differential-mode input Microelectronic Circuit Design McGraw-Hill Chap 15 - 34

MOSFET Differential Amplifiers: DC Analysis (Example) • Problem:Find Q-points of transistors in the differential amplifier. • Given data:VDD=VSS=12 V, ISS =200 mA, RSS = 500 kW, RD = 62 kW,l = 0.0133 V-1, Kn = 5 mA/ V2, VTN =1V • Analysis: To maintain pinch-off operation of M1 for nonzero VIC , Microelectronic Circuit Design McGraw-Hill Chap 15 - 35

MOSFET Differential Amplifiers: Differential-mode Input Signals Source node in differential amplifier represents virtual ground Differential-mode gain for balanced output is Gain for single-ended output is Microelectronic Circuit Design McGraw-Hill Chap 15 - 36

MOSFET Differential Amplifiers: Common-mode Input Signals Electronic current source is modeled by twice its small-signal output resistance representing output resistance of the current source. Common-mode half-circuit is similar to inverting amplifier with 2RSS as source resistor. Thus, common-mode conversion gain= 0 Due to infinite current gain of FET, ro can be neglected. Microelectronic Circuit Design McGraw-Hill Chap 15 - 37

Common-Mode Rejection ratio (CMRR) • For purely common-mode input signal, output of balanced MOS amplifier is zero, CMRR is infinite. For single-ended output, • RSS (which is much > REE and thus provides more Q-point stability) should be maximized. • To compare MOS amplifier directly to BJT amplifier, assume that MOS amplifier is biased by • From given data in example, MOS amplifier’s CMRR=54 or 35 dB (almost 10 dB worse than BJT amplifier).To increase CMRR in BJT and FET amplifiers, current sources with higher RSS or REE are used. Microelectronic Circuit Design McGraw-Hill Chap 15 - 38

Two-port model for Differential Amplifiers Two-port model simplifies circuit analysis of differential amplifiers. Expressions for FET are obtained by substituting RSS for REE. Microelectronic Circuit Design McGraw-Hill Chap 15 - 39

Differential Amplifier Design (Example) • Problem:Find Q-points of transistors in the differential amplifier. • Given data:Adm=40 dB, Rid >250 kW,single-ended CMRR> 80 dB, VICat least ±5V, MOSFETs with: l = 0.0133 V-1, Kn’ = 50 mA/ V2, VTN =1V, • BJTs with : bF =100, VA =75V, IS =0.5 fA • Assumptions: Active-region operation, symmetrical power supplies, bo = bF, vid maximum of ±30 mV. • Analysis: • Adm=40 dB =100. To achieve this gain with resistively loaded amplifier, we use BJT. For Adm = gm RC =40 IC RC , required gain can be obtained with voltage drop of 2.5 V across RC. • For bipolar differential amplifier, Rid =2rp, so, rp =125 kW. Microelectronic Circuit Design McGraw-Hill Chap 15 - 40

Differential Amplifier Design (Example contd.) Choose IC = 15 mA to provide safety margin. So RC =2.5 V/15 mA =167 kW. Choose RC = 180 kW as the nearest value with 5% toleranceand alos to compensate for neglecting ro in the analysis. VICof 5V requires collector voltage to be at least 5 V at all times. We also know that vid can be a maximum of ±30 mV for linearity. So ac component of differential output will not be greater than 100(0.03 V)=3V, half of which appears at each collector. Thus dc signal across RC won’t exceed 4 V( 2.5 V dc + 1.5 V ac) and positive power supply must fulfill Choose VCC=10 V to dive desired margin of 1 V, For symmetrical supplies, VEE = -10 V. Single-ended CMRR of 80 dB needs Choose current source with IEE =30 mA and REE > 20 MW Microelectronic Circuit Design McGraw-Hill Chap 15 - 41

Two-stage Prototype of an Op Amp • For higher gain, pnp C-E amplifier is connected at output of the input stage differential amplifier. • Virtual ground at emitter node allows input stage to achieve full inverting amplifier gain without needing emitter bypass capacitor. • Pnp transistor permits direct coupling between stages, allows emitter of pnp to be connected to ac ground and provides required voltage level shift to bring output back to zero. • Bypass and coupling capacitors are thus eliminated. Differential amplifier provides desired differential input,CMRR and ground referenced output as the input stage of op amp. Microelectronic Circuit Design McGraw-Hill Chap 15 - 42

Two-stage Op Amp: DC Analysis This circuit requires a resistance in series with emitter of Q3 to stabilize Q-point (as collector current of Q3 is exponentially dependent on base-emitter voltage), at the expense of voltage gain loss. From dc equivalent circuit, IE1= IE2 = I1 /2. If base current of Q3 is neglected and C-B current gains are one, As both inputs are zero, output also=0 IS3 is saturation current. For zero offset voltage Microelectronic Circuit Design McGraw-Hill Chap 15 - 43

Two-stage Op Amp: AC Analysis (Differential Mode) Half-circuit can be constructed from ac equivalent circuit in spite of asymmetricity, as voltage variations at collector of Q2 don’t substantially alter transistor current in forward-active operation region. From small-signal circuit model, Microelectronic Circuit Design McGraw-Hill Chap 15 - 44

Two-stage Op Amp: AC Analysis (Differential Mode contd.) This can be rewritten as Base current of Q3 is neglected so, IC2RC=VBE3=0.7 V, IC3R=VEE, Upper limit onIC2 and I1 is set by maximum dc bias current at input, lower limit on IC3 is set by minimum current to drive total load impedance at output. Microelectronic Circuit Design McGraw-Hill Chap 15 - 45

Two-stage Op Amp: AC Analysis (Common Mode) From ac equivalent circuit for common-mode inputs, For differential-mode inputs, collector current was Thus, From ac equivalent circuit, we observe that circuitry beyond collector of Q2 is same as that in differential mode half-circuit. The difference in collector currents causes difference in output voltage. Microelectronic Circuit Design McGraw-Hill Chap 15 - 46

Improving Op Amp Voltage Gain Overall amplifier gain decreases rapidly as the quiescent current of second stage decreases. Voltage gain can improve if resistor in second stage is replaced by current source with R2 >> ro3, if R2 is neglected, This expression can be reduced to Output resistance is degraded, amplifier more represents transconductance amplifier than a true low output resistance voltage amplifier. Microelectronic Circuit Design McGraw-Hill Chap 15 - 47

Reducing Output Resistance From ac equivalent circuit, A C-C stage is added to the prototype to maintain voltage gain but reduce output resistance. Microelectronic Circuit Design McGraw-Hill Chap 15 - 48

Three-Stage Bipolar Op Amp Analysis • Problem: Find differential-mode gain, CMRR, input and output resistances. • Given data:VCC=VEE=15 V, bo1 = bo2 = bo3 = bo4 =100, VA3 =75V, I1 = 100 mA, I2 = 500 mA, I3 = 5 mA, R1 = 750 kW , RL = 2 kW, R2 and R3 are infinite. • Analysis: Voltage at node 3 is one base-emitter voltage drop above zero. VEC3=15-0.7=14.3 V. Microelectronic Circuit Design McGraw-Hill Chap 15 - 49

Three-Stage Bipolar Op Amp Analysis (contd.) Overall gain is lower because of lower gain of first stage (since rp3 << RC) and lower gain than expected for second stage (as reflected loading of RL is of same order as ro3). Microelectronic Circuit Design McGraw-Hill Chap 15 - 50