FPGA konfiguravimas

290 likes | 466 Vues

FPGA konfiguravimas. Programuojamos mikrosistemos. FPGA. Konfiguracija.

FPGA konfiguravimas

E N D

Presentation Transcript

FPGA konfiguravimas Programuojamos mikrosistemos

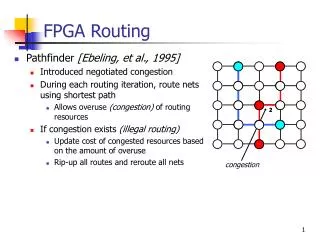

FPGA. Konfiguracija • Tam, kad programuojamoji struktūra atliktų reikiamą funkciją, sudaroma loginė schema, kuri išpildoma naudojant atitinkamus konkrečios FPGA (Spartan-3E) vidinius blokus (LUT, MUX, registrus, daugintuvus ir t.t.) ir juos tinkamai sujungus programuojamais sujungimais. Programuojami sujungimai

FPGA. Konfiguracija • FPGA - programuojami ventilių masyvai. Programavimas – ventilių masyvo elementų būsenų nustatymas. Kiekvieno elemento būsenai nusakyti reikalingas 1 bitas atminties. • Naudojant gamintojo programinę įrangą, schema (funkcija) transformuojama į binarinį failą (su plėtiniu .bit), kurio pagalba konfiguruojami matricos elementai. • BIT failas gali būti ‘užkrautas’ tiesiogiai į FPGA (pvz., per JTAG) arba gali būti įrašytas į papildomą atmintinę (PROM ar atminties kortelę).

FPGA. Konfiguracija VHDL kodas Struktūrinė schema architecture MLU_DATAFLOW of MLU is signal A1:STD_LOGIC; signal B1:STD_LOGIC; signal Y1:STD_LOGIC; signal MUX_0, MUX_1, MUX_2, MUX_3: STD_LOGIC; begin A1<=A when (NEG_A='0') else not A; B1<=B when (NEG_B='0') else not B; Y<=Y1 when (NEG_Y='0') else not Y1; MUX_0<=A1 and B1; MUX_1<=A1 or B1; MUX_2<=A1 xor B1; MUX_3<=A1 xnor B1; with (L1 & L0) select Y1<=MUX_0 when "00", MUX_1 when "01", MUX_2 when "10", MUX_3 when others; end MLU_DATAFLOW;

FPGA. Konfiguravimo technologijos • Saugikliai (fuse) • Antisaugikliai (Anti-fuse) • SRAM • EEPROM (FLASH) • EPROM

FPGA. Konfiguravimo technologijos. Saugikliai • Gamybos metu visi įmanomi sujungimai padaromi aktyvūs. Programavimo metu naudojant geerokai aukštesnę įtampą nei darbiniame režime (~18 V) nereikalingi sujungimai nudeginami.

FPGA. Konfiguravimo technologijos. Antisaugikliai • Prieš programavimą visi sujungimai būna atjungti (varža > 100 k) Programuojant suardoma dielektrinė struktūra ir kontakto varža sumažėja iki 500

FPGA. Konfiguravimo technologijos. Antisaugikliai • Prieš programavimą visi sujungimai būna atjungti (varža > 100 k) Programuojant suardoma dielektrinė struktūra ir kontakto varža sumažėja iki 500

FPGA. Konfiguravimo technologijos. Antisaugikliai • Privalumai: • Maži gabaritai (~1m) • Maža “off” talpa ir maža “on” varža. Tai sąlygoja mažą energijos sunaudojimą • Nereikia perprogramuoti išjungus maitinimą • Nereikia išorinės atminties programos saugojimui • Atsparūs radiacijai • Trūkumai: • Sudėtinga gamybos technologija • Nėra galimybės perprogramuoti

FPGA. Konfiguravimo technologijos. SRAM • Kiekvienas bitas SRAM technologijoje saugomas keturių tranzistorių struktūroje. Ši struktūra turi dvi stabilais būsenas kurios atitinka 0 ir 1. Papildomai dar reikia dviejų tranzistorių šios struktūros aptarnavimui. Taigi tipinei SRAM celei reikia 6 MOSFET tranzistorių vienio bito saugojimui.

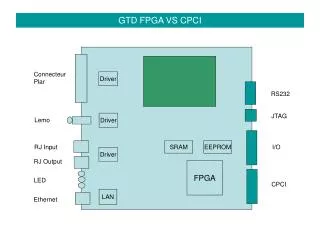

FPGA. Konfiguravimo technologijos. SRAM • Privalumai: • Labai tinkama projektavimui ir prototipams • Perrašymų skaičius neribotas • SRAM celės kuriamos ta pačia technologija, kaip ir likusi lusto dalis • Paprasta konstrukcija • Trūkumai: • Reikia užkrauti konfigūraciją kiekvieną kartą padavus maitinimą (tam reikia papildomos energetiškai nepriklausomos atminties arba mikroprocesoriaus). • Dideli SRAM celės gabaritai (6-12 tranzistorių) • Didelis (lyginant su kitomis technologijomis) galios suvartojimas dėl nuotėkio srovių tranzistoriuose

FPGA. Konfiguravimo technologijos. EEPROM • Elektriškai trinama programuojamoji atmintis (electrically erasable programmable read-only memory) Programavimo metu tarp užtūros ir santakos paduodama gerokai didesnė įtampa už darbinę. ‘Plaukiojanti’ užtūra įgyja neigiamą krūvį ir tranzistorius lieka atidarytas iki ‘ištrynimo’. Atrasis tranzistorius naudojamas informacijos ištrynimui (EPROM reikia UV spindulių)

FPGA. Konfiguravimo technologijos. EEPROM • Privalumai: • Energetiškai nepriklausomi • Pasiruošę darbui tik padavus maitinimą • E2PROM celė fiziškai mažesnė už SRAM celę. Todėl galimi trumpesni sujungimai. • Mažesnė nuotėkio srovė, dėl mažesnio tranzistorių skaičiaus • Trūkumai: • Sudėtinga gamybos technologija. • Didelė “on” varža • Vėlinimas dviem kartais blogesnis negu SRAM • Reikalinga didesnė rašymo įtampa (on-chip charge pump) • Rašymas apie 3 kart ilgesnis negu SRAM technologijos.

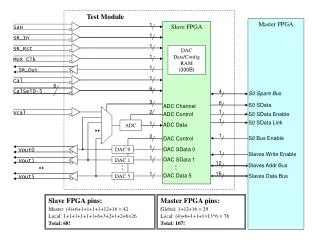

FPGA. SRAM konfiguravimas • SRAM pagrindu veikianti FPGA turi būti programuojama neišimant jos iš sistemos – “in system programming”. Ji perprogramuojama kiekvieną kartą įjungiant maitinimą. Tam kad visa sistema veiktų autonomiškai, šalia FPGA montuojama ir atminties mikroschema. • Visos SRAM celės jungiamos į vieną postūmio registrą ir programos failas į jį įrašomas nuosekliai. Esant reikalui galima jungti kelias FPGA nuosekliai ir jas programuoti vienu metu. Tokiu pat būdu galima ir nuskaityti įrašytą konfiguraciją. • SRAM celės gali būti grupuojamos į “freimus”

FPGA. Konfiguravimo režimai • Konfiguruojant FPGA gali būti taikomi keli programavimo režimai. Naudojamas režimas nurodomas nustatant atitinkamas būsenas tam skirtuose kontaktuose.

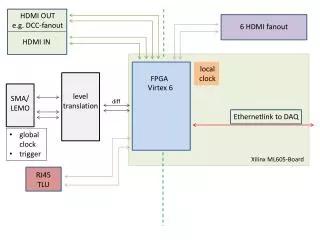

FPGA. Konfiguravimo režimai Xilinx PROMs: Slave/Master Serial Slave/Master SelectMAP Xilinx Cables: JTAG Slave Serial Slave SelectMAP FPGA Microprocessor: JTAG Slave Serial Slave SelectMAP Commodity Flash: Slave SelectMAP SPI* BPI* *SPI and BPI support is available in Spartan™-6, Virtex™-6, and some older FPGA families

FPGA konfiguravimo procesas • Atliekant konfiguravimą būtina žinoti apie: • Konfiguravimo kontaktus – konfiguravimo režimui nustatyti • Kai kurie konfiguravimo kontaktai yra įėjimai (būsenos jungikliai), kai kurie išėjimai (būsenos indikatoriai) • Konfigūravimo režimus • Priklausomai nuo konfiguravimo režimo reikia atitinkamai ‘suvaldyti’ konfiguravimo kontaktus ir kitą valdymo logiką (grandynus) • Skirtingi deerinimo (debugging) režimai sąlygoja skirtingus konfiguravimo režimus, kurie gali būti naudojami netgi vienu metu

Konfiguravimo kontaktai • Konfiguravimo metu naudojami specializuoti kontaktai • Mode pins • PROGRAM_B • CCLK (configuration clock) • INIT_B • DONE • DIN • DOUT • ... • Kai kurių kontaktų signalų kryptis (iėjimas ar išėjimas) priklauso nuo konfiguravimo režimo (Pvz. CCLK) • Kai kurie kontaktai naudojami tik spec. Konfiguravimo režimuose

Konfiguravimo režimai • Nuoseklus (Serial) • JTAG • Rekomenduojamas visiem prototipų projektavimo etapams. Naudojamas specialus JTAG kabelis • Master Serial • Valdymo signalus generuoja FPGA, naudojami nuoseklios sasajos atmintinės (Platform Flash PROM) • Slave Serial • Valdymo signalus generuoja išorinis įrenginys (mikroprocesorius, PC ar CPLD) • SPI (Serial Peripheral Interface) • Procesą valdo FPGA. Naudojamas SPI Flash PROM • Lygiagretus (naudojamos 8-bitųarba 16-bitųmagistralės) • Master SelectMAP • Procesą valdo FPGA • Slave SelectMAP • Valdymo signalus generuoja išorinis įrenginys • BPI (Byte-Wide Peripheral Interface) • Procesą valdo FPGA. Naudojamas NOR Flash

JTAG konfiguravimo režimas • Konfiguracinis filas (bitstream) saugomas kompiuteryje ir naudojant spec. programinę įrangą (ISE™)persiunčiamas tiesiai į FPGA • Valdymo signalai siunčiami lygiagrečiai, konfiguracija - nuosekliai TCK ISE + Cable FPGA FPGA FPGA TDI TDO TDO TMS TDO

Master Serial Configuration Mode • Master Serial mode • FPGA išduoda CCLK signa;ą • Įrašomas 1 bitas per CCLK • Duomenys saugomi išorinėje atmintyje (serial PROM) • Lėtas bet lengviausiai realizuojamas/valdomas • FPGA valdymo kontrolė • Visi konfiguravimo režimo nustatymo signalai žemame lygyje CCLK

Slave Serial Configuration Mode • Reikia išorinio CCLK signalų generatoriaus: • Mikroprocesorius arba mikrocontroleris • Nuoseklus Xilinx duomenų kabelis/jungtis • Kitas FPGA • Nuoseklioji FPGA jungtis • Įrašomas 1 bitas per viena CCLK ciklą • Visi konfiguravimo režimo valdymo signalai nustatyti į aukštą lygį. Serial Data FPGA Data CCLK Control Logic

Slave Serial Configuration Mode • Nuoseklus FPGA jungimas

Master SelectMap Mode (Master Paralel) • FPGA atlieka valdymo funkciją • FPGA valdo adresų magistralę • Perduodamas 1 baitas1 adresui • 8 CCLK ciklaibaitui • Didelis konfiguravimo greitis CCLK

Slave SelectMap Mode (Salve Paralel) • Reikia išorinio valdiklio (mikroprocesorius, Xilinx EPC,kitas FPGA, CPLD) • Ready/Busy bendravimo protokolas • Perduodamas 1 baitas • Išorinis įrenginys formuoja tiek atminties tiek konfiguruojamo FPGA valdymo signalus • Naudojant Xilinx Platform Flash XL nereikia naudoti papildomo konfiguravimo įrenginio FPGA Byte-Wide Data Data Ready/Busy Control Signals Control Logic