Booth Algorithm for Multiplier

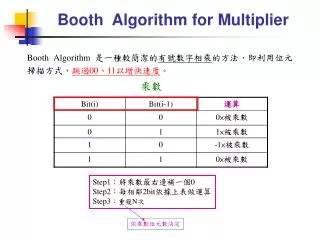

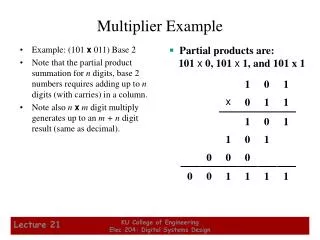

Booth Algorithm for Multiplier. Booth Algorithm 是一種較簡潔的 有號數字相乘 的方法,即利用位元掃描方式, 跳過 00 、 11 以增快速度 。. 乘數. Step1 :將乘數最右邊補一個 0 Step2 : 每相鄰 2bit 依據上表做運算 Step3 :重複 N 次. 依乘數位元數決定. Bit(i). Bit(i-1). 運算. 0. 0. 0× 被乘數. 0. 1. 1× 被乘數. 1. 0. -1× 被乘數. 1. 1. 0× 被乘數. Example.

Booth Algorithm for Multiplier

E N D

Presentation Transcript

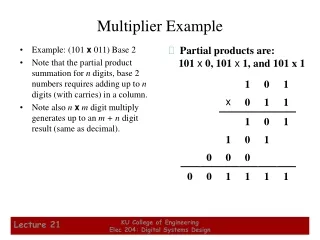

Booth Algorithm for Multiplier Booth Algorithm 是一種較簡潔的有號數字相乘的方法,即利用位元掃描方式,跳過00、11以增快速度。 乘數 Step1:將乘數最右邊補一個0 Step2:每相鄰2bit依據上表做運算 Step3:重複N次 依乘數位元數決定

Bit(i) Bit(i-1) 運算 0 0 0×被乘數 0 1 1×被乘數 1 0 -1×被乘數 1 1 0×被乘數 Example 範例:7 × -3 = -21 0111 → 0 1 1 1 → 0 1 1 1 × 11010 × 0 -1 1 -1 × 0 -1 1 -1 1 1 1 1 1 0 0 1 0 0 0 0 1 1 1 1 1 1 0 0 1 +0 0 0 0 0 1 1 1 0 1 0 1 1 = -21 (for 2’s) 2’s

Bit(i) Bit(i-1) 運算 0 0 0×被乘數 0 1 1×被乘數 1 0 -1×被乘數 1 1 0×被乘數 Algorithm 1b 1a 2

10 01 1b 1a 2 Example 範例: -3 (1101) × 7 (0111) = -21 (11101011) (A-M)

A Booth Algorithm B p CLK RESET Verilog Code (1) module Booth16(CLK, RESET, A, B, P); parameter WIDTH = 16; input CLK, RESET; input [WIDTH-1:0]A, B; output [WIDTH+WIDTH-1:0]P; reg [WIDTH+WIDTH-1:0]P; reg [WIDTH-1:0]Count; reg [WIDTH+WIDTH:0]PB; always@(posedge CLK or negedge RESET) begin if(!RESET) begin P = 0; Count = 0; PB = 0; end 定義輸入、輸出和 所需的Register 清除內部Reg

Verilog Code (2) else begin PB[WIDTH+WIDTH:0] = {16'd0, B, 1'b0}; for(Count = 0; Count < WIDTH; Count = Count + 1) begin casez(PB[1:0]) 2'b01: begin PB[WIDTH+WIDTH:WIDTH+1] = PB[WIDTH+WIDTH:WIDTH+1] + A[WIDTH-1:0]; begin if(PB[WIDTH+WIDTH] == 0) //最高位元為0,則補入的值為0. PB[WIDTH+WIDTH:0] = {1'b0, PB[WIDTH+WIDTH:1]}; else PB[WIDTH+WIDTH:0] = {1'b1, PB[WIDTH+WIDTH:1]}; end end 相當Algorithm中 {A, Q, Q-1} 執行16次 A ← A + M SAR

Verilog Code (3) 2'b10: begin PB[WIDTH+WIDTH:WIDTH+1] = PB[WIDTH+WIDTH:WIDTH+1] - A[WIDTH-1:0]; begin if(PB[WIDTH+WIDTH] == 0) PB[WIDTH+WIDTH:0] = {1'b0, PB[WIDTH+WIDTH:1]}; else PB[WIDTH+WIDTH:0] = {1'b1, PB[WIDTH+WIDTH:1]}; end end A ← A - M SAR

Verilog Code (4) default: begin if(PB[WIDTH+WIDTH] == 0) PB[WIDTH+WIDTH:0] = {1'b0, PB[WIDTH+WIDTH:1]}; else PB[WIDTH+WIDTH:0] = {1'b1, PB[WIDTH+WIDTH:1]}; end endcase end end P[WIDTH+WIDTH-1:0] = PB[WIDTH+WIDTH:1]; end endmodule 00/11 SAR 最後將內部Reg值傳至輸出