Logic Design Part 1: Multiplexers and More

140 likes | 161 Vues

Learn about multiplexers, encoders, logic functions, and Shannon's decomposition in logic design. Implement various MUX configurations using gates and explore the application of Shannon's theorem.

Logic Design Part 1: Multiplexers and More

E N D

Presentation Transcript

Lecture 24: Logic Design (Part 1) PROF. INDRANIL SENGUPTA DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

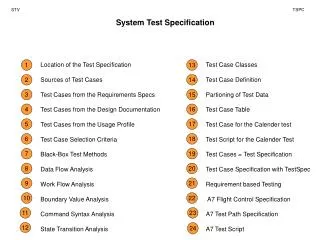

Introduction • We shall discuss some of the common functional blocks used in logic design. • We shall discuss the following: • Multiplexer • Decoder / Demultiplexer • Encoder • Comparator

Data Selectors or Multiplexers • A multiplexer is an electronic switch that has: • A set of n data input lines D = {D0, D1, …, Dn-1} • A set of m select input lines S = {S0, S1, …, Sm-1} • One output line f • One of the input data lines is connected to the output depending upon the value of the select lines (f = D0 if S = 0, f = D1 if S = 1, f = D2 if S = 2, and so on). • Usually, n = 2m. • Also called a 2m-to-1 multiplexer.

D0 2m-to-1 MUX D1 f Dn-1 S0 S1 Sm-1

Implement a 2-to-1 MUX using Gates D0 2-to-1 MUX f D1 S0 f = S0’.D0 + S0.D1

Implement a 4-to-1 MUX using Gates D0 4-to-1 MUX D1 f D2 D3 S0 S1 f = S1’.S0’.D0 + S1’.S0.D1 + S1.S0’.D2 + S1.S0.D3

Implement a 4-to-1 MUX using 2-to-1 MUX-es D0 2-to-1 MUX D1 2-to-1 MUX f S0 D2 2-to-1 MUX S1 D3 S0

Implement a 8-to-1 MUX using Smaller MUX-es D0 D4 4-to-1 MUX 4-to-1 MUX D1 D5 D2 D6 2-to-1 MUX D3 D7 f S0 S1 S2

Implement Logic Functions using MUX • Implement an n-variable function using 2n-to-1 MUX. • Connect the n variables to the select lines. • Connect the truth table output column values to data inputs.

Implement an n-variable function using 2n-1-to-1 MUX. • Connect (n-1) variables to the select lines. • Apply the remaining variable, its complement, 0 or 1 to the data inputs. • For this, we partition the truth table into groups of two rows each. D0 4-to-1 MUX D1 f D2 D3 S0 S1

D0 8-to-1 MUX D1 D2 D3 f D4 D5 D6 D7 S2 S0 S1

Implement Arbitrary Functions using 2-to-1 MUX • We repeatedly split a function into two smaller sub-functions by using Shannon’s decomposition theorem. • Shannon’s Decomposition Theorem: • An n-variable function f (x1, x2, …, xn) can be decomposed with respect to any of the n variables (say, x1) as: f (x1, x2, …, xn) = x1’.f (0, x2, …, xn) + x1. f (1, x2, …, xn) = x1’.f10 + x1.f11 • Each application of Shannon’s decomposition theorem is like using a 2-to-1 MUX: • Apply x1to the select inputs, and f10 and f11 to the data inputs.

An Example Worked Out Given function: f = A’.B + B.C + A.C’ Expanding w.r.t. A, we get: f = A’.(B + B.C) + A.(B.C + C’) = A’.(B) + A.(B + C’) Expanding (B + C’) w.r.t. B, we get: B + C’ = B’.(C’) + B.(1)